Interrupter synchronization question

dexter, Thu Aug 28 2014, 07:10AMCurrently i'm rebuilding my SSTC to handle more power than previously. Because of this i want to synchronize the interrupter signal with the coil resonant frequency to avoid hard switching. So i'll be using a D type flip-flop between the interrupter and gate drive IC.

In all the circuits i found the interrupter signal is connected to RST pin of the flip-flop while keeping D pin high but this will result in synchronization only on high to low transitions of the interrupter. I'm a bit concerned about this because it might result in quite short on times for the first half cycle which might create problems for the IGBT's...

So why not connect the interrupter signal to the D pin of the flip-flop and held CLR high so that both low to high and high to low interrupter transitions get synchronized with the coil resonant frequency and avoid those possible low on times?

Or it doesn't matter because the moment the interrupter goes high will be the moment the coil will start osculating so the low to high interrupter transition will always be synchronized regardless of the presence/absence of a flip-flop?

Re: Interrupter synchronization question

Steve Conner, Thu Aug 28 2014, 07:28AM

Yes, the low to high transition of the interrupter signal is what starts the oscillations, so it can't be synchronised. There is no clock signal to synchronise it to until the oscillations have started.

Steve Conner, Thu Aug 28 2014, 07:28AM

Yes, the low to high transition of the interrupter signal is what starts the oscillations, so it can't be synchronised. There is no clock signal to synchronise it to until the oscillations have started.

Re: Interrupter synchronization question

dexter, Thu Aug 28 2014, 07:42AM

thanks Steve

I got mis-leaded when i tested my circuit because i used a signal generator tor the clock input and that why i saw the lack of synchronization on the low to high interrupter transition...

dexter, Thu Aug 28 2014, 07:42AM

thanks Steve

I got mis-leaded when i tested my circuit because i used a signal generator tor the clock input and that why i saw the lack of synchronization on the low to high interrupter transition...

Re: Interrupter synchronization question

Sigurthr, Thu Aug 28 2014, 01:10PM

If you'll indulge my thinking out loud...

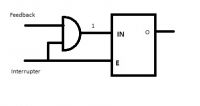

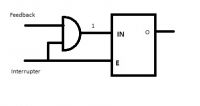

I've always wondered why the use of a D FlipFlop instead of an AND gate.

The only thing I can figure is that this would pulse the enable at the feedback frequency. To stop the enable being switched at fres you'd have to add a buffer on the feedback branch going to the AND gate and place a RC filter after the buffer that holds the signal above the switching transition voltage while feedback is present but doesn't extend the fall times by so much that you lose synchronization. This might be very difficult to do though.

That brings up why not just AND feedback and interrupter and feed that into gate drive input and just hold enable HIGH with a pull up. It should still transition HIGH to LOW as normal but with no feedback going to the AND gate there may not be a LOW to HIGH initialization.

You could pass raw interrupter to Enable instead of using pull up and this should provide the oscillation startup ping like normal. I think this would work as the normal state is no feedback signal and a LOW to HIGH on the Enable line causes an oscillation ping which starts feedback.

So if my train of thought is correct then a replacement for the D FlipFlop would be an AND gate to synchronize feedback and interrupter signals and feed raw interrupter to Enable as normal.

What do you think?

Sigurthr, Thu Aug 28 2014, 01:10PM

If you'll indulge my thinking out loud...

I've always wondered why the use of a D FlipFlop instead of an AND gate.

The only thing I can figure is that this would pulse the enable at the feedback frequency. To stop the enable being switched at fres you'd have to add a buffer on the feedback branch going to the AND gate and place a RC filter after the buffer that holds the signal above the switching transition voltage while feedback is present but doesn't extend the fall times by so much that you lose synchronization. This might be very difficult to do though.

That brings up why not just AND feedback and interrupter and feed that into gate drive input and just hold enable HIGH with a pull up. It should still transition HIGH to LOW as normal but with no feedback going to the AND gate there may not be a LOW to HIGH initialization.

You could pass raw interrupter to Enable instead of using pull up and this should provide the oscillation startup ping like normal. I think this would work as the normal state is no feedback signal and a LOW to HIGH on the Enable line causes an oscillation ping which starts feedback.

So if my train of thought is correct then a replacement for the D FlipFlop would be an AND gate to synchronize feedback and interrupter signals and feed raw interrupter to Enable as normal.

What do you think?

Re: Interrupter synchronization question

Sigurthr, Thu Aug 28 2014, 01:16PM

If you'll indulge my thinking out loud...

I've always wondered why the use of a D FlipFlop instead of an AND gate.

The only thing I can figure is that this would pulse the enable at the feedback frequency. To stop the enable being switched at fres you'd have to add a buffer on the feedback branch going to the AND gate and place a RC filter after the buffer that holds the signal above the switching transition voltage while feedback is present but doesn't extend the fall times by so much that you lose synchronization. This might be very difficult to do though.

That brings up why not just AND feedback and interrupter and feed that into gate drive input and just hold enable HIGH with a pull up. It should still transition HIGH to LOW as normal but with no feedback going to the AND gate there may not be a LOW to HIGH initialization.

You could pass raw interrupter to Enable instead of using pull up and this should provide the oscillation startup ping like normal. I think this would work as the normal state is no feedback signal and a LOW to HIGH on the Enable line causes an oscillation ping which starts feedback.

So if my train of thought is correct then a replacement for the D FlipFlop would be an AND gate to synchronize feedback and interrupter signals and feed raw interrupter to Enable as normal.

What do you think?

Sigurthr, Thu Aug 28 2014, 01:16PM

If you'll indulge my thinking out loud...

I've always wondered why the use of a D FlipFlop instead of an AND gate.

The only thing I can figure is that this would pulse the enable at the feedback frequency. To stop the enable being switched at fres you'd have to add a buffer on the feedback branch going to the AND gate and place a RC filter after the buffer that holds the signal above the switching transition voltage while feedback is present but doesn't extend the fall times by so much that you lose synchronization. This might be very difficult to do though.

That brings up why not just AND feedback and interrupter and feed that into gate drive input and just hold enable HIGH with a pull up. It should still transition HIGH to LOW as normal but with no feedback going to the AND gate there may not be a LOW to HIGH initialization.

You could pass raw interrupter to Enable instead of using pull up and this should provide the oscillation startup ping like normal. I think this would work as the normal state is no feedback signal and a LOW to HIGH on the Enable line causes an oscillation ping which starts feedback.

So if my train of thought is correct then a replacement for the D FlipFlop would be an AND gate to synchronize feedback and interrupter signals and feed raw interrupter to Enable as normal.

What do you think?

Re: Interrupter synchronization question

dexter, Thu Aug 28 2014, 02:12PM

if this is the circuit you are talking about then it will not work

the waveform will look something like this

F _____──__──__──______──__â” €â”€__──______──__──__──___

I ____ _─────────______─────⠔€â”€â”€â”€_______─────────____

1 _____──__──__─_______──__──__â ”€_______──__──__─_____

O _____──__â ”€â”€__─_______──__──__─_______──_ _──__─_____

so you will have hard switching so no synchronization

a flip-flop is used because it transfers data present at D pin on a low to high clock transition, the same happens with CLR pin. By holding D high all the time and controlling RST with the interrupter signal a constant HIGH will be present at output when interrupter is high and when the interrupter goes low the output will go low only on a low to high clock transition aka synchronization

dexter, Thu Aug 28 2014, 02:12PM

if this is the circuit you are talking about then it will not work

the waveform will look something like this

F _____──__──__──______──__â” €â”€__──______──__──__──___

I ____ _─────────______─────⠔€â”€â”€â”€_______─────────____

1 _____──__──__─_______──__──__â ”€_______──__──__─_____

O _____──__â ”€â”€__─_______──__──__─_______──_ _──__─_____

so you will have hard switching so no synchronization

a flip-flop is used because it transfers data present at D pin on a low to high clock transition, the same happens with CLR pin. By holding D high all the time and controlling RST with the interrupter signal a constant HIGH will be present at output when interrupter is high and when the interrupter goes low the output will go low only on a low to high clock transition aka synchronization

Re: Interrupter synchronization question

Sigurthr, Thu Aug 28 2014, 03:28PM

Aha, I see now, the on time of the last pulse in the train isn't transfered. Thanks a ton for the detailed explanation!

My coils have all been overengineered to eat hard switching so I haven't needed the interrupter synch, but I'd always wondered if there was a smaller footprint and lower parts count alternative.

It looks like even if you found a scheme of discretes and/or gates to do what we want it would end up being more complex and parts heavy than the flip flop.

Sigurthr, Thu Aug 28 2014, 03:28PM

Aha, I see now, the on time of the last pulse in the train isn't transfered. Thanks a ton for the detailed explanation!

My coils have all been overengineered to eat hard switching so I haven't needed the interrupter synch, but I'd always wondered if there was a smaller footprint and lower parts count alternative.

It looks like even if you found a scheme of discretes and/or gates to do what we want it would end up being more complex and parts heavy than the flip flop.

Print this page