PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Thu Sept 05 2013, 03:31PMHello,

I have built a rather large, CW-running SSTC. It uses a 4046 with Phase comparator 2, which is always 0° in lock, and a feedback from secondary base current (1:30 CT on a high permeability ferrite core). I have built a smaller SSTC previously with this PLL type and it ran well, but I am having some problems with this big one...

When I dial it up, it always locks well, but when I try to draw an arc to ground, it makes just 1 spark and the output disappears. When this happens, the VCO "slams" to its highest programmed frequency and sits there. Only resetting the supply will make it work again.

Has anyone encountered this problem? What you think might help to solve it? I will try modifying the PLL feedback time constant (right now it is 10k and 22n) and maybe also the CT, but as the driver is built on a PCB (I thought it would run well so I made a "final version" without previous testing), I would not want to mess it up.

Thanks, Jan

Edit: I have displayed the signal input (pin 14) versus the VCO output on the scope and replicated the problem. What happens is that the output LEADS the input by at least 30 degrees. Why does the PLL not decrease the frequency then, when the phase is not zero and output leads the input ??

Another edit: I forgot to mention that pins 4 (VCO out) and 3 (comparator IN) are connected together.

The VCO range is around 60-100 kHz and the resonant frequency is around 80-85 kHz.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Sigurthr, Fri Sept 06 2013, 08:07AM

I had a similar issue with mine. I never found the cause but I narrowed the frequency range and that seemed to fix it. Ground strikes would still pull it off resonance but it wouldn't stall out after the ground arc extinguished.

Sigurthr, Fri Sept 06 2013, 08:07AM

I had a similar issue with mine. I never found the cause but I narrowed the frequency range and that seemed to fix it. Ground strikes would still pull it off resonance but it wouldn't stall out after the ground arc extinguished.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 08:34AM

It seems to be a glitch in the IC itself. During the "error condition" the phase pulses output indicates that the PLL is not locked, but the comparator output does not do anything to fix it.

I tried another IC manufacturer and it didn't work at all it got messed up just when I plugged in the secondary base with no voltage on the bridge (probably some voltage induced from the gate drive) and the output was at the highest frequency all the time.

it got messed up just when I plugged in the secondary base with no voltage on the bridge (probably some voltage induced from the gate drive) and the output was at the highest frequency all the time.

Dr. Dark Current, Fri Sept 06 2013, 08:34AM

It seems to be a glitch in the IC itself. During the "error condition" the phase pulses output indicates that the PLL is not locked, but the comparator output does not do anything to fix it.

I tried another IC manufacturer and it didn't work at all

it got messed up just when I plugged in the secondary base with no voltage on the bridge (probably some voltage induced from the gate drive) and the output was at the highest frequency all the time.

it got messed up just when I plugged in the secondary base with no voltage on the bridge (probably some voltage induced from the gate drive) and the output was at the highest frequency all the time.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Fri Sept 06 2013, 09:04AM

With secondary base current feedback, I think it is possible for the phase of the feedback to swing a full 180 degrees under heavy loading. That would make it impossible for a PLL to stay locked.

The Type-2 phase comparator in the 4046 is edge-triggered, so it's a really bad choice for use around a Tesla coil. It could be falsely triggered by switching spikes from the bridge, or HF hash from ground arcs. If it tries to lock to its own switching spikes, it will jump to one end of the VCO range.

The Type-1 works on the average value of the XORed signals, so it naturally rejects spikes. If you add an integrator to the loop, it behaves the same as the Type-2, except for the 90 degree phase difference, which can be dealt with in a number of ways. I once did it by using a capacitor as the feedback CT burden.

Steve Conner, Fri Sept 06 2013, 09:04AM

With secondary base current feedback, I think it is possible for the phase of the feedback to swing a full 180 degrees under heavy loading. That would make it impossible for a PLL to stay locked.

The Type-2 phase comparator in the 4046 is edge-triggered, so it's a really bad choice for use around a Tesla coil. It could be falsely triggered by switching spikes from the bridge, or HF hash from ground arcs. If it tries to lock to its own switching spikes, it will jump to one end of the VCO range.

The Type-1 works on the average value of the XORed signals, so it naturally rejects spikes. If you add an integrator to the loop, it behaves the same as the Type-2, except for the 90 degree phase difference, which can be dealt with in a number of ways. I once did it by using a capacitor as the feedback CT burden.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

GeordieBoy, Fri Sept 06 2013, 09:14AM

I was also just about to reply, but just noticed Steve's reply pop up that already said most of what I was going to write!

I'd just second that the Type-2 sequential-logic phase detector is incredibly sensitive to any glitches on the signals being fed in.

It basically acts to adjust the VCO until you have the same number of rising edges per second on it's signal and reference inputs. i.e. It tries to get the frequency right first, then it tries to force the rising edges to be in phase.

When you attempt to draw an arc it's likely that the secondary base feedback signal is getting contaminated with all sorts of crap. The type-2 phase comparator will see all of these additional "edges per second" on the feedback signal from the secondary and interpret this as a big increase in frequency compared to the reference. Then it will do what it's been trained to do. Try to increase the VCO frequency until the frequencies match. That is why I think the type-2 detector will have pumped the VCO up to the maximum frequency limit.

As steve said the Type-1 (EXOR) phase detector is a much better choice in this application because it's inherently more immune to noise, and will work well with squared-up input waveforms. Although it is designed to lock with 90 deg phase shift, you can easily introduce an additional 90 degree shift into the secondary base current sensing waveform by terminating it into a capacitance or inductance instead of a current sensing resistor. The two 90 degree phase shifts add up to 180 degrees, so you just invert one of the signals into the phase-comparator to get it to now lock at 0 degrees.

If you insist on trying to use Type-2 phase detector you'll have to get both of the input signals really clean of any spurious edges. Probably using filtering and comparators with hysteresis, but the phase shifts introduced will likely undo much of the perceived benefit of using the type-2 detector anyway.

-Richie,

GeordieBoy, Fri Sept 06 2013, 09:14AM

I was also just about to reply, but just noticed Steve's reply pop up that already said most of what I was going to write!

I'd just second that the Type-2 sequential-logic phase detector is incredibly sensitive to any glitches on the signals being fed in.

It basically acts to adjust the VCO until you have the same number of rising edges per second on it's signal and reference inputs. i.e. It tries to get the frequency right first, then it tries to force the rising edges to be in phase.

When you attempt to draw an arc it's likely that the secondary base feedback signal is getting contaminated with all sorts of crap. The type-2 phase comparator will see all of these additional "edges per second" on the feedback signal from the secondary and interpret this as a big increase in frequency compared to the reference. Then it will do what it's been trained to do. Try to increase the VCO frequency until the frequencies match. That is why I think the type-2 detector will have pumped the VCO up to the maximum frequency limit.

As steve said the Type-1 (EXOR) phase detector is a much better choice in this application because it's inherently more immune to noise, and will work well with squared-up input waveforms. Although it is designed to lock with 90 deg phase shift, you can easily introduce an additional 90 degree shift into the secondary base current sensing waveform by terminating it into a capacitance or inductance instead of a current sensing resistor. The two 90 degree phase shifts add up to 180 degrees, so you just invert one of the signals into the phase-comparator to get it to now lock at 0 degrees.

If you insist on trying to use Type-2 phase detector you'll have to get both of the input signals really clean of any spurious edges. Probably using filtering and comparators with hysteresis, but the phase shifts introduced will likely undo much of the perceived benefit of using the type-2 detector anyway.

-Richie,

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 09:14AM

Steve, this is a (SR)SSTC, so the bridge should always switch in phase with the secondary base current. I would not be surprised that much if it lost lock during ground strikes, but why does it latch to the highest frequency and sits there after all the arcs have disappeared?

Well, the noise also came to my mind, I will try adding a 100 pf capacitor in parallel to the signal input pin. Anyways the driver is shielded in a grounded metal enclosure, so interference should be suppressed...

Thanks for the replies so far

Dr. Dark Current, Fri Sept 06 2013, 09:14AM

Steve, this is a (SR)SSTC, so the bridge should always switch in phase with the secondary base current. I would not be surprised that much if it lost lock during ground strikes, but why does it latch to the highest frequency and sits there after all the arcs have disappeared?

Well, the noise also came to my mind, I will try adding a 100 pf capacitor in parallel to the signal input pin. Anyways the driver is shielded in a grounded metal enclosure, so interference should be suppressed...

Thanks for the replies so far

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

GeordieBoy, Fri Sept 06 2013, 09:27AM

When you arc the top of the secondary to ground it's like you are short-circuiting the secondary coil. So other higher-frequency modes of the secondary that you don't normally think about are probably getting excited. For instance the 3/4 wave mode of the secondary will likely be close to the 3rd harmonic of your inverter so will now get pumped up.

If there's significant 3rd harmonic content in the measured secondary base current this will cause many more zero crossing edges to be seen by the phase comparator. Again, the Type-2 phase comparator will interpret these additional edges as a sudden increase in the frequency of the feedback signal and attempt to ramp up the VCO frequency to match it.

-Richie,

GeordieBoy, Fri Sept 06 2013, 09:27AM

When you arc the top of the secondary to ground it's like you are short-circuiting the secondary coil. So other higher-frequency modes of the secondary that you don't normally think about are probably getting excited. For instance the 3/4 wave mode of the secondary will likely be close to the 3rd harmonic of your inverter so will now get pumped up.

If there's significant 3rd harmonic content in the measured secondary base current this will cause many more zero crossing edges to be seen by the phase comparator. Again, the Type-2 phase comparator will interpret these additional edges as a sudden increase in the frequency of the feedback signal and attempt to ramp up the VCO frequency to match it.

-Richie,

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 10:28AM

I also thought about exciting some harmonics, but the measurements confirm that during the fault condition, the base current is lagging the inverter output so it "wants to" tune to a lower frequency.

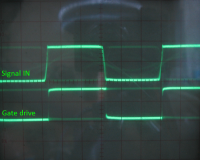

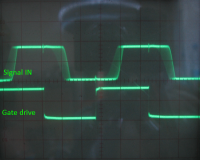

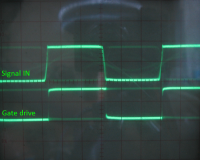

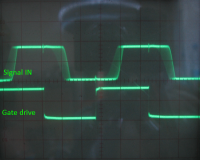

Here are some scope shots

1. Normal operation, arcing to air, it will work even with the metal cover of the driver removed. The primary current (not shown) is a sine wave with switching transitions near zero current. 10V/div, 2us/div

2. The fault condition - no arcs, output not connected to anything. The gate drive output (almost identical with VCO output) leads the signal input by nearly 90 degrees, primary current (not shown) is a triangle wave. Putting the cover on the driver makes no difference, as well as adding a 33 pf capacitor in parallel to the signal input. There is some switching noise on the signal input, but it is below the CMOS input threshold and might as well be interference the scope picks up. The VCO input voltage is equal to Vcc and the PC output is held in a low impedance high state.

The phase pulses output as well indicates that the PLL is not locked, but the comparator output does nothing, just sits high... I don't know, it looks like a bug in the IC to me

Dr. Dark Current, Fri Sept 06 2013, 10:28AM

I also thought about exciting some harmonics, but the measurements confirm that during the fault condition, the base current is lagging the inverter output so it "wants to" tune to a lower frequency.

Here are some scope shots

1. Normal operation, arcing to air, it will work even with the metal cover of the driver removed. The primary current (not shown) is a sine wave with switching transitions near zero current. 10V/div, 2us/div

2. The fault condition - no arcs, output not connected to anything. The gate drive output (almost identical with VCO output) leads the signal input by nearly 90 degrees, primary current (not shown) is a triangle wave. Putting the cover on the driver makes no difference, as well as adding a 33 pf capacitor in parallel to the signal input. There is some switching noise on the signal input, but it is below the CMOS input threshold and might as well be interference the scope picks up. The VCO input voltage is equal to Vcc and the PC output is held in a low impedance high state.

The phase pulses output as well indicates that the PLL is not locked, but the comparator output does nothing, just sits high... I don't know, it looks like a bug in the IC to me

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

ScotchTapeLord, Fri Sept 06 2013, 03:20PM

I don't mean to hijack but I have a question and this thread is relevant to my current work. I'm using the type 2 pll comparator for primary feedback for my DRSSTC. After reading this I'm wondering if it's worth pursuing. Is it likely that I will run into similar problems?

ScotchTapeLord, Fri Sept 06 2013, 03:20PM

I don't mean to hijack but I have a question and this thread is relevant to my current work. I'm using the type 2 pll comparator for primary feedback for my DRSSTC. After reading this I'm wondering if it's worth pursuing. Is it likely that I will run into similar problems?

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 03:37PM

Hi, well it is possible that you will face the same problem.

Most likely it has really something to do with the switching noise from the bridge getting back into the IC, even though it doesn't show up on the scope... Why it messes up only after a ground strike - I don't know, but possibly it has something to do with the phase difference, once the inverter starts leading the signal input (eg. after the feedback is disrupted by a ground strike), the spikes are in different positions which the IC can't deal with.

And I also found it depends on the manufacturer of the IC. Texas instruments does what I described, ONsemi doesn't work at all.

Dr. Dark Current, Fri Sept 06 2013, 03:37PM

Hi, well it is possible that you will face the same problem.

Most likely it has really something to do with the switching noise from the bridge getting back into the IC, even though it doesn't show up on the scope... Why it messes up only after a ground strike - I don't know, but possibly it has something to do with the phase difference, once the inverter starts leading the signal input (eg. after the feedback is disrupted by a ground strike), the spikes are in different positions which the IC can't deal with.

And I also found it depends on the manufacturer of the IC. Texas instruments does what I described, ONsemi doesn't work at all.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Avalanche, Fri Sept 06 2013, 04:06PM

I would think using primary feedback in a DRSSTC with phase comparator 2 would be a lot less risky, due to the strong resonance of the primary inductance and capacitance. You're measuring a strong current on something connected to the inverter. Noise pickup/spurious edge pickup can then be eliminated by normal EMC practices, like screening and board layout...

At least I hope the above is true for a DRSSTC as I'm also going to be using phase comparator 2 on mine

I never did find a good solid reliable feedback mechanism for an SSTC. I still have the opinion that every feedback SSTC works by complete fluke Even if you get a good feedback from the secondary base, the coil can shift the phase, or do whatever it feels like such as jump to a harmonic when you adjust the output.

Even if you get a good feedback from the secondary base, the coil can shift the phase, or do whatever it feels like such as jump to a harmonic when you adjust the output.

Avalanche, Fri Sept 06 2013, 04:06PM

I would think using primary feedback in a DRSSTC with phase comparator 2 would be a lot less risky, due to the strong resonance of the primary inductance and capacitance. You're measuring a strong current on something connected to the inverter. Noise pickup/spurious edge pickup can then be eliminated by normal EMC practices, like screening and board layout...

At least I hope the above is true for a DRSSTC as I'm also going to be using phase comparator 2 on mine

I never did find a good solid reliable feedback mechanism for an SSTC. I still have the opinion that every feedback SSTC works by complete fluke

Even if you get a good feedback from the secondary base, the coil can shift the phase, or do whatever it feels like such as jump to a harmonic when you adjust the output.

Even if you get a good feedback from the secondary base, the coil can shift the phase, or do whatever it feels like such as jump to a harmonic when you adjust the output.Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 04:25PM

Well, I made a PLL SSTC which worked perfectly, with 4046 PC2 and secondary base feedback. It was connected in the same way as this big TC. I could draw ground arcs few centimeters from the breakout point and it continued to work, there were no knobs, just turn it on and it works. No harmonics because of the limited VCO range.

But I'm really lost as to what to do with this one... It uses almost the same circuit, just the frequency is 3 times lower.

In the meantime I tried 2 other IC manufacturers - no difference. I tried modifying the PLL lowpass filter and various noise suppresion circuits on the INput terminal - no difference... The controller is shielded in a metal case and the 4046 supply is decoupled by an LC filter.

Dr. Dark Current, Fri Sept 06 2013, 04:25PM

Well, I made a PLL SSTC which worked perfectly, with 4046 PC2 and secondary base feedback. It was connected in the same way as this big TC. I could draw ground arcs few centimeters from the breakout point and it continued to work, there were no knobs, just turn it on and it works. No harmonics because of the limited VCO range.

But I'm really lost as to what to do with this one... It uses almost the same circuit, just the frequency is 3 times lower.

In the meantime I tried 2 other IC manufacturers - no difference. I tried modifying the PLL lowpass filter and various noise suppresion circuits on the INput terminal - no difference... The controller is shielded in a metal case and the 4046 supply is decoupled by an LC filter.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Fri Sept 06 2013, 05:24PM

One other observation: The PLL is trying to achieve zero phase shift between the drive voltage and the secondary base current, but if the secondary resonance is damped heavily enough, zero phase shift can't be obtained at any frequency. It follows that the PLL will just stick at one end of its tuning range.

Steve Conner, Fri Sept 06 2013, 05:24PM

One other observation: The PLL is trying to achieve zero phase shift between the drive voltage and the secondary base current, but if the secondary resonance is damped heavily enough, zero phase shift can't be obtained at any frequency. It follows that the PLL will just stick at one end of its tuning range.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Fri Sept 06 2013, 10:16PM

I just tried

-40106 Schmitt inverter before the signal input pin - no difference

-reversing the GDT and CT phasing, thinking that the interference might come from the bridge - no difference

So far I have tried at least 10 things, and it still behaves EXACTLY the same. It all points to a design fault inside the 4046 IC...

Edit: Do you know any other type 2 PLL ICs?

Dr. Dark Current, Fri Sept 06 2013, 10:16PM

I just tried

-40106 Schmitt inverter before the signal input pin - no difference

-reversing the GDT and CT phasing, thinking that the interference might come from the bridge - no difference

So far I have tried at least 10 things, and it still behaves EXACTLY the same. It all points to a design fault inside the 4046 IC...

Edit: Do you know any other type 2 PLL ICs?

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Sat Sept 07 2013, 01:57PM

I think I have found the problem by some more measurements. The phase comparator is getting confused. The VCO output leads the signal input by around 60 degrees, and instead of delaying the output by said 60 degrees, the PC is trying to quicken the output by 300 degrees - so it switches its output between H and high-impedance state. But because the VCO is already at its maximum frequency, this doesn't work.

Why do I think this - look at the attached scope shots. The Phase Pulses output is exactly the opposite to what it should be according to the data sheet.

So it seems the only fix to this problem is to stop using this phase comparator

Dr. Dark Current, Sat Sept 07 2013, 01:57PM

I think I have found the problem by some more measurements. The phase comparator is getting confused. The VCO output leads the signal input by around 60 degrees, and instead of delaying the output by said 60 degrees, the PC is trying to quicken the output by 300 degrees - so it switches its output between H and high-impedance state. But because the VCO is already at its maximum frequency, this doesn't work.

Why do I think this - look at the attached scope shots. The Phase Pulses output is exactly the opposite to what it should be according to the data sheet.

So it seems the only fix to this problem is to stop using this phase comparator

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

GeordieBoy, Mon Sept 09 2013, 02:03PM

If you really think the PLL chip is faulty, why don't you get two good quality adjustable square wave generators and do a bench test. Look at the output of the type-2 phase comparator on an oscilloscope for the following conditions:

1. Reference frequency is higher than Signal frequency (PC2 output permanently low)

2. Reference frequency is lower than Signal frequency (PC2 output permanently high)

3. Frequencies are the same but Reference leads Signal in phase (PC2 output pulsing low)

4. Frequencies are the same but Reference lags Signal in phase (PC2 output pulsing high)

5. Frequencies are the same and signals are almost perfectly in phase (PC2 output tri-stated most of the time)

If you do this with accurately controlled *CLEAN* squarewaves in a workbench test scenario you should be able to tell if your 4046 IC is damaged or has a design flaw.

-Richie,

GeordieBoy, Mon Sept 09 2013, 02:03PM

It all points to a design fault inside the 4046 IC......or more likely a problem with your circuit design. The 4046 IC has been successfully used to implement phase-locked loops in the electronics industry for donkey's years! If you design something that marginally works with one manufacturer's part and fails completely with another manufacturer, then this should set alarm bells ringing that your circuit might not be operating the chip properly as intended.

The phase comparator is getting confused. The VCO output leads the signal input by around 60 degrees, and instead of delaying the output by said 60 degrees, the PC is trying to quicken the output by 300 degrees - so it switches its output between H and high-impedance state. But because the VCO is already at its maximum frequency, this doesn't work.The type-2 phase comparator is getting confused by HF noise or harmonics present on the signal input. As I said before both inputs need to be perfectly clean square waves with no chattering (bouncing) at the rising and falling edges. Any double edges (or lingering of the input in the "no man's land" between logic '0' and logic '1') will cause the type-2 phase comparator to think that the signal input is higher frequency than the VCO and set the charge-pump to command the VCO to a higher frequency.

Why do I think this - look at the attached scope shots. The Phase Pulses output is exactly the opposite to what it should be according to the data sheet.

If you really think the PLL chip is faulty, why don't you get two good quality adjustable square wave generators and do a bench test. Look at the output of the type-2 phase comparator on an oscilloscope for the following conditions:

1. Reference frequency is higher than Signal frequency (PC2 output permanently low)

2. Reference frequency is lower than Signal frequency (PC2 output permanently high)

3. Frequencies are the same but Reference leads Signal in phase (PC2 output pulsing low)

4. Frequencies are the same but Reference lags Signal in phase (PC2 output pulsing high)

5. Frequencies are the same and signals are almost perfectly in phase (PC2 output tri-stated most of the time)

If you do this with accurately controlled *CLEAN* squarewaves in a workbench test scenario you should be able to tell if your 4046 IC is damaged or has a design flaw.

-Richie,

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Mon Sept 09 2013, 03:49PM

Yes. The input amplifier on the 4046 only has about 16mV (IIRC) of hysteresis, so it doesn't take much to trigger a double transition. The waveform you showed has slow edges and looks a bit dirty, so I think it could easily do it.

My cure was to use PC1 where the multiple transitions don't matter.

Steve Conner, Mon Sept 09 2013, 03:49PM

Yes. The input amplifier on the 4046 only has about 16mV (IIRC) of hysteresis, so it doesn't take much to trigger a double transition. The waveform you showed has slow edges and looks a bit dirty, so I think it could easily do it.

My cure was to use PC1 where the multiple transitions don't matter.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

GeordieBoy, Mon Sept 09 2013, 07:59PM

It goes something like this:

1. Input A goes high first

2. So the phase comparator output goes high because input B needs to catch up!

3. The toggling of PC2 output impresses a brief pulse through the threshold of the input B

4. Phase comparator 2 sees this rising edge and thinks that input B has now caught up, so tri-states its output immediately!

5. The real rising edge of the input B signal comes along some time later

6. Now phase comparator 2 has seen *TWO* rising edges on input B so it thinks input B frequency is too high!

7. PC2 output now goes low to tell input B to slow down!!! *NOTE*

8. This state persists until the next rising edge on input A

*Note that this final state (between step 7 & 8) is the exact opposite of what it should be to make the lagging input B signal catch up with the leading input A reference. Input B needs to go faster, not slow down.

This isn't speculation or just something that is theoretically possible. I observed it happening with a 4046 PLL IC using PC2 in a practical application. The key to curing it is to keep the rising and falling edges of both signals really fast, really clean, and the source impedance nice and low.

PC1 does only give you a guaranteed 90 degree phase at the mid-point of the frequency locking range though. So the phase will vary across the full locking range though.

-Richie,

GeordieBoy, Mon Sept 09 2013, 07:59PM

Yes. The input amplifier on the 4046 only has about 16mV (IIRC) of hysteresis, so it doesn't take much to trigger a double transition. The waveform you showed has slow edges and looks a bit dirty, so I think it could easily do it.Yes, very small hysteresis and very fast acting. I've even seen the fast-slewing output from the phase-comparator2 itself toggling state capacitively couple a tiny spike onto a slowly changing high-impedance input waveform! This then changes the state of the PC2 output immediately.

It goes something like this:

1. Input A goes high first

2. So the phase comparator output goes high because input B needs to catch up!

3. The toggling of PC2 output impresses a brief pulse through the threshold of the input B

4. Phase comparator 2 sees this rising edge and thinks that input B has now caught up, so tri-states its output immediately!

5. The real rising edge of the input B signal comes along some time later

6. Now phase comparator 2 has seen *TWO* rising edges on input B so it thinks input B frequency is too high!

7. PC2 output now goes low to tell input B to slow down!!! *NOTE*

8. This state persists until the next rising edge on input A

*Note that this final state (between step 7 & 8) is the exact opposite of what it should be to make the lagging input B signal catch up with the leading input A reference. Input B needs to go faster, not slow down.

This isn't speculation or just something that is theoretically possible. I observed it happening with a 4046 PLL IC using PC2 in a practical application. The key to curing it is to keep the rising and falling edges of both signals really fast, really clean, and the source impedance nice and low.

My cure was to use PC1 where the multiple transitions don't matter.That's what I would recommend too. Use PC1 and phase-shift the current-sense signal by 90degrees by terminating it into a reactive burden. Or alternatievely, phase-shift the VCO output by 90 degrees using that trick where you synthesise it at 4x frequency and divide it down into two quadrature "gray code" outputs.

PC1 does only give you a guaranteed 90 degree phase at the mid-point of the frequency locking range though. So the phase will vary across the full locking range though.

-Richie,

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Tue Sept 10 2013, 07:47AM

PC2 is really a switched-mode integrator because its tri-state output allows the capacitor to hold its charge. This makes the loop second-order, giving 0 degrees phase offset throughout the lock range.

You can achieve the same thing by replacing PC1's loop filter with an op-amp integrator. You get a constant 90 degrees phase offset throughout the lock range. This is how my Mk2 PLL drivers worked. I got rid of the 90 degree phase shift by running the VCO at twice the output frequency and dividing it down in quadrature with a couple of flip-flops.

A second-order loop has some quite unpleasant implications for stability of a regular PLL that has to lock to an independent oscillator. But in the Tesla coil application, the PLL is locking to a phase-shifted version of its own output. This means the loop is really only about 1.5 orders so the stability problems are greatly eased.

Technically the loop is still second-order because the Tesla resonator can introduce a 90 degree phase lag at high frequencies. But this is still much less of a problem than the process of locking two independent oscillators, which behaves like an integrator and adds a 90 degree lag at all frequencies.

Steve Conner, Tue Sept 10 2013, 07:47AM

PC2 is really a switched-mode integrator because its tri-state output allows the capacitor to hold its charge. This makes the loop second-order, giving 0 degrees phase offset throughout the lock range.

You can achieve the same thing by replacing PC1's loop filter with an op-amp integrator. You get a constant 90 degrees phase offset throughout the lock range. This is how my Mk2 PLL drivers worked. I got rid of the 90 degree phase shift by running the VCO at twice the output frequency and dividing it down in quadrature with a couple of flip-flops.

A second-order loop has some quite unpleasant implications for stability of a regular PLL that has to lock to an independent oscillator. But in the Tesla coil application, the PLL is locking to a phase-shifted version of its own output. This means the loop is really only about 1.5 orders so the stability problems are greatly eased.

Technically the loop is still second-order because the Tesla resonator can introduce a 90 degree phase lag at high frequencies. But this is still much less of a problem than the process of locking two independent oscillators, which behaves like an integrator and adds a 90 degree lag at all frequencies.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

GeordieBoy, Tue Sept 10 2013, 02:15PM

Hi Steve,

Thanks for that explanation. I remember chatting about this some time ago and you had eluded to the fact that the PLL design requirements to properly track the resonant frequency of a TC were in contradiction to what you would normally do to implement clock recovery or motor speed control by PLL.

Now it's clear why. The VCO in a clock recovery PLL (or motor in a speed control application) acts like an integrator itself, because you feed it a voltage, to get a frequency (or speed) but what you are measuring and attempting to control is it's phase (or position.) Hence the integration because phase or position is the time integral of frequency or speed.

So for a conventional PLL the whole loop will be second order because of one pole from the loop filter and one from the integrator action of the VCO or motor. But for a TC you don't get that pole from the plant because the output frequency *HAS* to be the same as the drive frequency. Therefore you can increase the order of the overall loop to minimise steady-state error by going to PC2 that has integrator action built in.

Cheers,

-Richie,

PS. I had a student last year trying to make a modern recreation of a Baird Televisor who had trouble locking the speed of a permanent magnet DC motor to the sync pulses of the incoming video. She has a lot of trouble with motor noise on the PLL input from an IR light-gate, causing the PC2 to act up. If someone chooses the same project again this year I'll get them to try PC1 with an additional integrator to force phase error to zero. Getting loop stability is quite a challange for them though, because of the poles of the loop filter, speed-to-phase conversion, motor L/R, and the inertia of the Nipkow disc! It makes students have to think though!

GeordieBoy, Tue Sept 10 2013, 02:15PM

Hi Steve,

Thanks for that explanation. I remember chatting about this some time ago and you had eluded to the fact that the PLL design requirements to properly track the resonant frequency of a TC were in contradiction to what you would normally do to implement clock recovery or motor speed control by PLL.

Now it's clear why. The VCO in a clock recovery PLL (or motor in a speed control application) acts like an integrator itself, because you feed it a voltage, to get a frequency (or speed) but what you are measuring and attempting to control is it's phase (or position.) Hence the integration because phase or position is the time integral of frequency or speed.

So for a conventional PLL the whole loop will be second order because of one pole from the loop filter and one from the integrator action of the VCO or motor. But for a TC you don't get that pole from the plant because the output frequency *HAS* to be the same as the drive frequency. Therefore you can increase the order of the overall loop to minimise steady-state error by going to PC2 that has integrator action built in.

Cheers,

-Richie,

PS. I had a student last year trying to make a modern recreation of a Baird Televisor who had trouble locking the speed of a permanent magnet DC motor to the sync pulses of the incoming video. She has a lot of trouble with motor noise on the PLL input from an IR light-gate, causing the PC2 to act up. If someone chooses the same project again this year I'll get them to try PC1 with an additional integrator to force phase error to zero. Getting loop stability is quite a challange for them though, because of the poles of the loop filter, speed-to-phase conversion, motor L/R, and the inertia of the Nipkow disc! It makes students have to think though!

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Tue Sept 10 2013, 02:42PM

Yes, that's it exactly! If you want to use a second-order loop in an ordinary PLL application, you have to insert a zero in the loop filter to get any phase margin whatsoever. Otherwise you have two integrators in the feedback loop and a phase margin of 0.

If you want to use a second-order loop in an ordinary PLL application, you have to insert a zero in the loop filter to get any phase margin whatsoever. Otherwise you have two integrators in the feedback loop and a phase margin of 0.

I haven't done an analog PLL in a while, but recently I did a few second-order digital ones with IIR loop filters. I think of the loop filter as a PI controller, where the P term provides the zero for stability.

These arguments about poles and zeros only hold when the circuit is running in its linear region, but the process by which the PLL gets into lock in the first place is highly nonlinear. So the second-order loop has more finicky capture behaviour that can include conditional stability. Again not relevant to Tesla coil applications because the loop is never "out of lock" in the sense that an ordinary PLL can get out of lock. The two frequencies going into the phase detector are always the same, so it can always produce a non-zero output on average.

Steve Conner, Tue Sept 10 2013, 02:42PM

Yes, that's it exactly!

If you want to use a second-order loop in an ordinary PLL application, you have to insert a zero in the loop filter to get any phase margin whatsoever. Otherwise you have two integrators in the feedback loop and a phase margin of 0.

If you want to use a second-order loop in an ordinary PLL application, you have to insert a zero in the loop filter to get any phase margin whatsoever. Otherwise you have two integrators in the feedback loop and a phase margin of 0.I haven't done an analog PLL in a while, but recently I did a few second-order digital ones with IIR loop filters. I think of the loop filter as a PI controller, where the P term provides the zero for stability.

These arguments about poles and zeros only hold when the circuit is running in its linear region, but the process by which the PLL gets into lock in the first place is highly nonlinear. So the second-order loop has more finicky capture behaviour that can include conditional stability. Again not relevant to Tesla coil applications because the loop is never "out of lock" in the sense that an ordinary PLL can get out of lock. The two frequencies going into the phase detector are always the same, so it can always produce a non-zero output on average.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Tue Sept 10 2013, 05:38PM

Guys, I have found the problem, but still not sure how to cure it.

The IC is not really faulty, it is just more complex than it seemed at first.

My problem is not the noise. It is the fact, that the Phase Comparator 2 has a "memory" which is 2 cycles, or 720 degrees "long". The 74HC4046 datasheet (which is not really the same IC, but the principle is the same) tells us, that the demodulated output voltage when using the PC2 depends on a phase difference of the signals from -360 to +360 degrees.

So what happens when there is a missing pulse on the input? The input signal phase has changed by 360 degrees. The input and VCO signals are still in phase, but the Phase Comparator sees this as a 360 degree shift and tries to correct it by actually delaying or advancing the VCO output by + or - 360 degrees (depends on where exactly the next pulse after the missing one comes). However, because the Tesla Coil system doesn't allow such a large phase shift within the VCO frequency range, the PLL will never lock the phase again unless the input is disrupted once more (for example by resetting the supply voltage). In an open-loop system such as an FM demodulation, this is not a problem, because the VCO output and PC input signals are not frequency-linked.

As for the different behavior of another IC manufacturer... Either that IC is somewhat damaged (as I have tried 3 more manufacturers and all behave exactly the same as the TI one), or it has different architecture which causes additional problems.

P.S. The missing pulse was just an example, during a ground spark there may be several missing, distorted, or wrong-frequency pulses. But if the signals (after the resonance is possible again) catch up with the wrong phase (+- 360 degrees), there the problem comes.

Dr. Dark Current, Tue Sept 10 2013, 05:38PM

Guys, I have found the problem, but still not sure how to cure it.

The IC is not really faulty, it is just more complex than it seemed at first.

My problem is not the noise. It is the fact, that the Phase Comparator 2 has a "memory" which is 2 cycles, or 720 degrees "long". The 74HC4046 datasheet (which is not really the same IC, but the principle is the same) tells us, that the demodulated output voltage when using the PC2 depends on a phase difference of the signals from -360 to +360 degrees.

So what happens when there is a missing pulse on the input? The input signal phase has changed by 360 degrees. The input and VCO signals are still in phase, but the Phase Comparator sees this as a 360 degree shift and tries to correct it by actually delaying or advancing the VCO output by + or - 360 degrees (depends on where exactly the next pulse after the missing one comes). However, because the Tesla Coil system doesn't allow such a large phase shift within the VCO frequency range, the PLL will never lock the phase again unless the input is disrupted once more (for example by resetting the supply voltage). In an open-loop system such as an FM demodulation, this is not a problem, because the VCO output and PC input signals are not frequency-linked.

As for the different behavior of another IC manufacturer... Either that IC is somewhat damaged (as I have tried 3 more manufacturers and all behave exactly the same as the TI one), or it has different architecture which causes additional problems.

P.S. The missing pulse was just an example, during a ground spark there may be several missing, distorted, or wrong-frequency pulses. But if the signals (after the resonance is possible again) catch up with the wrong phase (+- 360 degrees), there the problem comes.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Tue Sept 10 2013, 07:16PM

Sounds like another vote for PC1 with an external integrator!

Steve Conner, Tue Sept 10 2013, 07:16PM

Sounds like another vote for PC1 with an external integrator!

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Tue Sept 10 2013, 07:44PM

Well, it seems I'l really have to leave this phase comparator alone, it doesn't look suitable to use in closed loop systems...

As for the PC1 with integrator: There are 2 possible problems - noise getting into the op amp and weak signal on the shunt capacitor. That's why I was trying to avoid this solution... The 4046 IC itself is pretty well immune to interference, I could run the coil with the cover of the driver off (for measurement purposes) and it ran just fine.

Dr. Dark Current, Tue Sept 10 2013, 07:44PM

Well, it seems I'l really have to leave this phase comparator alone, it doesn't look suitable to use in closed loop systems...

As for the PC1 with integrator: There are 2 possible problems - noise getting into the op amp and weak signal on the shunt capacitor. That's why I was trying to avoid this solution... The 4046 IC itself is pretty well immune to interference, I could run the coil with the cover of the driver off (for measurement purposes) and it ran just fine.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Tue Sept 10 2013, 07:53PM

I've built about 8 or 9 drivers using PC1 with an integrator. It works fine for me!

I didn't even bother trying PC2 because connecting a sensitive edge-triggered state machine to a Tesla coil looked like a really bad idea.

In a previous design I used a shunt capacitor on the CT. It worked great until I used it to drive a series resonant induction heater with feedback from the inverter output current. The RF current was too much for the capacitor and it exploded.

Steve Conner, Tue Sept 10 2013, 07:53PM

I've built about 8 or 9 drivers using PC1 with an integrator. It works fine for me!

I didn't even bother trying PC2 because connecting a sensitive edge-triggered state machine to a Tesla coil looked like a really bad idea.

In a previous design I used a shunt capacitor on the CT. It worked great until I used it to drive a series resonant induction heater with feedback from the inverter output current. The RF current was too much for the capacitor and it exploded.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Tue Sept 10 2013, 09:36PM

Haha

Steve, do you use an inverting amplifier after the integrator in the PLL filter? Or does it work to swap the PC inputs?

Dr. Dark Current, Tue Sept 10 2013, 09:36PM

Haha

Steve, do you use an inverting amplifier after the integrator in the PLL filter? Or does it work to swap the PC inputs?

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Wed Sept 11 2013, 08:02AM

This is the circuit I've been using since about 2005. It uses an inverting amplifier in the loop.

It uses an inverting amplifier in the loop.

I don't think you can swap the phase comparator inputs, because only one of the inputs has the amplifier and self-bias circuit. I use that to take the signal from the CT directly.

Steve Conner, Wed Sept 11 2013, 08:02AM

This is the circuit I've been using since about 2005.

It uses an inverting amplifier in the loop.

It uses an inverting amplifier in the loop. I don't think you can swap the phase comparator inputs, because only one of the inputs has the amplifier and self-bias circuit. I use that to take the signal from the CT directly.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Dr. Dark Current, Wed Sept 11 2013, 08:53AM

OK, thanks

Dr. Dark Current, Wed Sept 11 2013, 08:53AM

OK, thanks

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

RayeR, Thu Sept 12 2013, 01:53PM

Very interesting thread about PLL. About 10 years ago I was started to design my 1st PLL controller for DR-SSTC. That times was PLL usage very rare, most of coilers used just simple pickup antenna.

I had spent many hours playing with 74HC4046 and trying all 3 comparators. I found that PC1 worked best for me, Also maybe I failed with PC2 was due to noise because I started on universal board without shielding and then found how it is sensitive to RFI when power goes up...

Also I was messing with various phase shift issues. One thing I tried to add additional 90deg phase shift was connecting 2 PLLs in cascade with PC1 to get 90+90 but later I found I don't need this when using pickup antenna... I can see Steve is doing this by running 2f0 with divider. Probably better choice as it holds 90deg in whole range. I also found interesting the idea of integrator in the filter, maybe I'll try this in some new design but have much less time than before...

BTW did someone tried to implement fully digital PLL in some fast ARM MCU or FPGA logic?

RayeR, Thu Sept 12 2013, 01:53PM

Very interesting thread about PLL. About 10 years ago I was started to design my 1st PLL controller for DR-SSTC. That times was PLL usage very rare, most of coilers used just simple pickup antenna.

I had spent many hours playing with 74HC4046 and trying all 3 comparators. I found that PC1 worked best for me, Also maybe I failed with PC2 was due to noise because I started on universal board without shielding and then found how it is sensitive to RFI when power goes up...

Also I was messing with various phase shift issues. One thing I tried to add additional 90deg phase shift was connecting 2 PLLs in cascade with PC1 to get 90+90 but later I found I don't need this when using pickup antenna... I can see Steve is doing this by running 2f0 with divider. Probably better choice as it holds 90deg in whole range. I also found interesting the idea of integrator in the filter, maybe I'll try this in some new design but have much less time than before...

BTW did someone tried to implement fully digital PLL in some fast ARM MCU or FPGA logic?

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Steve Conner, Thu Sept 12 2013, 03:58PM

Yes, I believe Steve Ward and Phillip Slawinski's latest driver is a digital PLL running on some sort of fast microcontroller, and a few people are working on FPGA-based drivers at the moment.

A MCU has too much latency to run anything but a PLL, but a FPGA can emulate a traditional feedback driver too, possibly using digital filters for phase lead.

I stayed with my old driver because it worked fine and I couldn't be bothered designing a new one. I've nearly run out of PCBs though so maybe it is time to try something new.

I've nearly run out of PCBs though so maybe it is time to try something new.

Steve Conner, Thu Sept 12 2013, 03:58PM

Yes, I believe Steve Ward and Phillip Slawinski's latest driver is a digital PLL running on some sort of fast microcontroller, and a few people are working on FPGA-based drivers at the moment.

A MCU has too much latency to run anything but a PLL, but a FPGA can emulate a traditional feedback driver too, possibly using digital filters for phase lead.

I stayed with my old driver because it worked fine and I couldn't be bothered designing a new one.

I've nearly run out of PCBs though so maybe it is time to try something new.

I've nearly run out of PCBs though so maybe it is time to try something new.Re: PLL SSTC with Type 2 phase comparator problems (added some info)

RayeR, Thu Sept 19 2013, 11:25AM

Yeah, I already seen in another thread that they made some FPGA PLL design with fast ADC. I think FPGAs are very well suited for this purpose but they are still a bit blackbox for me. I would rather use some DSP which also have quite low latency and high throughput (due to multiple buses and special instructiuon) but they are expansive. But now there are many low cost and fast enough ARM MCUs that maybe also could handle it. So maybe for som future project...

RayeR, Thu Sept 19 2013, 11:25AM

Steve Conner wrote ...

Yes, I believe Steve Ward and Phillip Slawinski's latest driver is a digital PLL running on some sort of fast microcontroller, and a few people are working on FPGA-based drivers at the moment.

A MCU has too much latency to run anything but a PLL, but a FPGA can emulate a traditional feedback driver too, possibly using digital filters for phase lead.

Yes, I believe Steve Ward and Phillip Slawinski's latest driver is a digital PLL running on some sort of fast microcontroller, and a few people are working on FPGA-based drivers at the moment.

A MCU has too much latency to run anything but a PLL, but a FPGA can emulate a traditional feedback driver too, possibly using digital filters for phase lead.

Yeah, I already seen in another thread that they made some FPGA PLL design with fast ADC. I think FPGAs are very well suited for this purpose but they are still a bit blackbox for me. I would rather use some DSP which also have quite low latency and high throughput (due to multiple buses and special instructiuon) but they are expansive. But now there are many low cost and fast enough ARM MCUs that maybe also could handle it. So maybe for som future project...

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

Goodchild, Thu Sept 19 2013, 03:17PM

The cool thing about FPGAs is that they are not as much of a black box as you may thing! I learned VHDL in about a month not spending a whole lot of time. The thing that makes FPGA based design much better than MCU is not only the speed (100MHz+) but the parallel processing capability.

Let’s say you had an MCU that reads an ADC and then updates a timer based on that info, this may take many clocks (hundreds even) because the MCU can only do one thing at a time. First it would read the ADC then it would update the timer with a lot of little steps in between. With the FPGA this whole operation could be done potential in one clock cycle if coded correctly. On top of this it could also be doing several other things at the same time, like receiving serial data, all without impacting any other part of the device.

If anything I would say it simply takes a shift in thinking from traditional MCUs to program any kind of programmable logic. Although the code is c-like it functions a lot differently due to the parallel operation.

My FPGA based control uses a pipe line ADC running at the same speed as the FPGA. Basically every clock (100MHz) the ADC clocks 10 bits of data into the FPGA via a parallel pipeline interafce. One clock later the output changes as a direct result. That’s roughly a 20nS response time to any change in conduction. This is as fast as most analog units doing the same thing.

Goodchild, Thu Sept 19 2013, 03:17PM

The cool thing about FPGAs is that they are not as much of a black box as you may thing! I learned VHDL in about a month not spending a whole lot of time. The thing that makes FPGA based design much better than MCU is not only the speed (100MHz+) but the parallel processing capability.

Let’s say you had an MCU that reads an ADC and then updates a timer based on that info, this may take many clocks (hundreds even) because the MCU can only do one thing at a time. First it would read the ADC then it would update the timer with a lot of little steps in between. With the FPGA this whole operation could be done potential in one clock cycle if coded correctly. On top of this it could also be doing several other things at the same time, like receiving serial data, all without impacting any other part of the device.

If anything I would say it simply takes a shift in thinking from traditional MCUs to program any kind of programmable logic. Although the code is c-like it functions a lot differently due to the parallel operation.

My FPGA based control uses a pipe line ADC running at the same speed as the FPGA. Basically every clock (100MHz) the ADC clocks 10 bits of data into the FPGA via a parallel pipeline interafce. One clock later the output changes as a direct result. That’s roughly a 20nS response time to any change in conduction. This is as fast as most analog units doing the same thing.

Re: PLL SSTC with Type 2 phase comparator problems (added some info)

RayeR, Fri Sept 20 2013, 10:46AM

Yes. I didn't express well. The principles of FPGA, PLD, PLA... are known to me a quite long (I met them on university a little bit). I understand what advantages/disadvantages over MCU it has, you're right. But mostly I have a problem with thinking in parallel programming and VHDL. And there are some cathes like e.g. signal propagation issue in long counter structure and other limitations that don't exist in MCU world (MCU's has surely its different cathes :). Also I didn't saw there would be available some simple lightweight opensource/free developing environment like equivalent of GNU GCC tool chain that is widely spreaded over MCUs. I only saw that manufacturers are giving some demoversion of their bloatware limited to small designs. I also never physically programmed the FPGA and don't know what kind of programmer I need. I like e.g. programming of Atmel AVR MCUs because I just need 5 wires from my parallel port to do SPI programming.

Yeah I admit that's all due to my laziness but I didn't get the right motivation to study and use FPGAs more at work or elsewhere yet, and free time is very limited as I'm working now...

RayeR, Fri Sept 20 2013, 10:46AM

Goodchild wrote ...

The cool thing about FPGAs is that they are not as much of a black box as you may thing! I learned VHDL in about a month not spending a whole lot of time. The thing that makes FPGA based design much better than MCU is not only the speed (100MHz+) but the parallel processing capability...

The cool thing about FPGAs is that they are not as much of a black box as you may thing! I learned VHDL in about a month not spending a whole lot of time. The thing that makes FPGA based design much better than MCU is not only the speed (100MHz+) but the parallel processing capability...

Yes. I didn't express well. The principles of FPGA, PLD, PLA... are known to me a quite long (I met them on university a little bit). I understand what advantages/disadvantages over MCU it has, you're right. But mostly I have a problem with thinking in parallel programming and VHDL. And there are some cathes like e.g. signal propagation issue in long counter structure and other limitations that don't exist in MCU world (MCU's has surely its different cathes :). Also I didn't saw there would be available some simple lightweight opensource/free developing environment like equivalent of GNU GCC tool chain that is widely spreaded over MCUs. I only saw that manufacturers are giving some demoversion of their bloatware limited to small designs. I also never physically programmed the FPGA and don't know what kind of programmer I need. I like e.g. programming of Atmel AVR MCUs because I just need 5 wires from my parallel port to do SPI programming.

Yeah I admit that's all due to my laziness but I didn't get the right motivation to study and use FPGAs more at work or elsewhere yet, and free time is very limited as I'm working now...

Print this page