Why is the ucc27243 enable pin ignored on the use2.7?

Pac85hv, Fri Aug 04 2017, 03:49PMThe title covers most of it, why did they use and gates if they already had an enable pin?I'm planning to design a modified version which has the startup oscillator and those two and gates would came in handy.

Re: Why is the ucc27243 enable pin ignored on the use2.7?

Justin, Fri Aug 04 2017, 04:31PM

Here you go.

"The TL3116 is a fast comparator which overall acts as a zero cross detector, and the two ouputs (inverted and non-inverted) go into IC5 (AND gates) which go into the enable pins of the main drive circuit. This output also acts as a clock signal to the 74HC74 D Flip flop. The output of the flip-flop (Q) must be logic 1 for both the AND gates to send an output to the drive. The flip flop therefore acts as the control to turn on and off the drive, and this can be achieved by forcing Q to go high or low. We will see how the interrupter input turns on the drive signal, and this can be stopped by OCD, end of drive, or UVLO, all sycned to a zero-crossing by the flip-flop (where the output of Q only changes at the next rising clock edge).

One effect of this is that the flip-flop can only shut off the drive at rising clock edges, so depending on the phase of your feedback, it can either shut the drive at n cycles or 0.5+n cycles. This also means that the current can potentially grow for about 1.5 half-cycles at worse case, so you need to be aware of this and set your current limit conservatively.

Here's a back-of-the envelope rough example: Suppose my primary current ring up is more-or-less linear and rings up at about 100A every half cycle. I want to make sure my IGBTs see at most 1000A, and this will happen in 5 full cycles. At the worse case, it takes about 1.5 half cycles to trip the OCD, hence the OCD should be set at around 850A or so. This will lead to turn off after a peak current of either 900A or 1000A depending on CT phase."

Justin, Fri Aug 04 2017, 04:31PM

Pac85hv wrote ...

The title covers most of it, why did they use and gates if they already had an enable pin?I'm planning to design a modified version which has the startup oscillator and those two and gates would came in handy.

The title covers most of it, why did they use and gates if they already had an enable pin?I'm planning to design a modified version which has the startup oscillator and those two and gates would came in handy.

Here you go.

"The TL3116 is a fast comparator which overall acts as a zero cross detector, and the two ouputs (inverted and non-inverted) go into IC5 (AND gates) which go into the enable pins of the main drive circuit. This output also acts as a clock signal to the 74HC74 D Flip flop. The output of the flip-flop (Q) must be logic 1 for both the AND gates to send an output to the drive. The flip flop therefore acts as the control to turn on and off the drive, and this can be achieved by forcing Q to go high or low. We will see how the interrupter input turns on the drive signal, and this can be stopped by OCD, end of drive, or UVLO, all sycned to a zero-crossing by the flip-flop (where the output of Q only changes at the next rising clock edge).

One effect of this is that the flip-flop can only shut off the drive at rising clock edges, so depending on the phase of your feedback, it can either shut the drive at n cycles or 0.5+n cycles. This also means that the current can potentially grow for about 1.5 half-cycles at worse case, so you need to be aware of this and set your current limit conservatively.

Here's a back-of-the envelope rough example: Suppose my primary current ring up is more-or-less linear and rings up at about 100A every half cycle. I want to make sure my IGBTs see at most 1000A, and this will happen in 5 full cycles. At the worse case, it takes about 1.5 half cycles to trip the OCD, hence the OCD should be set at around 850A or so. This will lead to turn off after a peak current of either 900A or 1000A depending on CT phase."

Re: Why is the ucc27243 enable pin ignored on the use2.7?

Pac85hv, Fri Aug 04 2017, 04:57PM

But wouldn't the enable pins have the same effect?

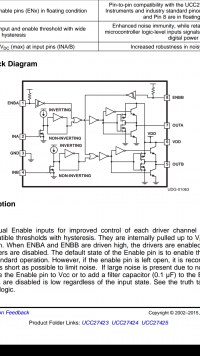

Here is a picture of the internal schematic:

If you consider pin 1 and 2:

Pin 2 is the signal input and it is inverted by the FET(and re inverted in the inverting version), pin one is also inverted and both are fed into a nor gate.

Feeding two inverted input to a nor gate is the same as feeding them directly to an and gate so the gate driver chip effectively acts like an and gate. The same happens for pins 4 and 8.

By hooking up the synched interrupt signal to the enable pins the same affect should be obtained so is there any reason it isn't actually like that?

Pac85hv, Fri Aug 04 2017, 04:57PM

But wouldn't the enable pins have the same effect?

Here is a picture of the internal schematic:

If you consider pin 1 and 2:

Pin 2 is the signal input and it is inverted by the FET(and re inverted in the inverting version), pin one is also inverted and both are fed into a nor gate.

Feeding two inverted input to a nor gate is the same as feeding them directly to an and gate so the gate driver chip effectively acts like an and gate. The same happens for pins 4 and 8.

By hooking up the synched interrupt signal to the enable pins the same affect should be obtained so is there any reason it isn't actually like that?

Re: Why is the ucc27243 enable pin ignored on the use2.7?

Chris_Dickey, Sat Aug 12 2017, 02:28AM

The default state of the UCC27423 needs to be output high, in order to turn on the N-channel FET in the power stage.

See the schematic here, whose power stage is identical to the UD2.7. The reason I refer to this instead of the UD2.7 is that the internal schematic of an FDD8424H is shown on Steve's schematic, but hidden on Loneoceans'. (UD2.7 schematic is here, about halfway down the page.)

I'll go through this for the first gate driver, since all 4 are identical.

The reason for doing this is twofold:

1. The power stage itself (Q3A, Q3B) is both similar to a CMOS inverter (thus, high input -> low output) and...

2. The P-channel (high-side, Q3B) FET is AC-coupled.

Because of this, the P-channel FET can only be driven on for a short period of time (t << RC = 100nF * 1kΩ = 100µs); it must default to off (R22 discharges C26 and the gate capacitance of Q3B).

The UCC driver's (IC9A) output goes low when the enable pin goes low. This would try to drive the P-channel FET's (Q3B) gate low through a capacitor (C26). This would make it pulse low (turning the FET on), then decay to high (turning the FET off) due to R22, causing the power stage to go high-impedance. This is not something you want to do to because then nothing is controlling the gate voltage of the IGBTs in the bridge (via GDT2 connector -> GDT -> bridge IGBTs). Also, the pulse high, might turn the bridge on and leave it on when the output goes high-impedance.

If you had some sort of strange gate driver IC whose output was high when disabled, you could use the enable function of it directly. However, because most gate driver ICs with enable pins go low when disabled (including the UCC27423), the easier solution is to always have the UCC27423 driver enabled and to apply some logic gates to the inputs.

Chris_Dickey, Sat Aug 12 2017, 02:28AM

The default state of the UCC27423 needs to be output high, in order to turn on the N-channel FET in the power stage.

See the schematic here, whose power stage is identical to the UD2.7. The reason I refer to this instead of the UD2.7 is that the internal schematic of an FDD8424H is shown on Steve's schematic, but hidden on Loneoceans'. (UD2.7 schematic is here, about halfway down the page.)

I'll go through this for the first gate driver, since all 4 are identical.

The reason for doing this is twofold:

1. The power stage itself (Q3A, Q3B) is both similar to a CMOS inverter (thus, high input -> low output) and...

2. The P-channel (high-side, Q3B) FET is AC-coupled.

Because of this, the P-channel FET can only be driven on for a short period of time (t << RC = 100nF * 1kΩ = 100µs); it must default to off (R22 discharges C26 and the gate capacitance of Q3B).

The UCC driver's (IC9A) output goes low when the enable pin goes low. This would try to drive the P-channel FET's (Q3B) gate low through a capacitor (C26). This would make it pulse low (turning the FET on), then decay to high (turning the FET off) due to R22, causing the power stage to go high-impedance. This is not something you want to do to because then nothing is controlling the gate voltage of the IGBTs in the bridge (via GDT2 connector -> GDT -> bridge IGBTs). Also, the pulse high, might turn the bridge on and leave it on when the output goes high-impedance.

If you had some sort of strange gate driver IC whose output was high when disabled, you could use the enable function of it directly. However, because most gate driver ICs with enable pins go low when disabled (including the UCC27423), the easier solution is to always have the UCC27423 driver enabled and to apply some logic gates to the inputs.

Re: Why is the ucc27243 enable pin ignored on the use2.7?

dexter, Fri Aug 18 2017, 09:09AM

for some odd reason i bought non inverting gate drive IS's for my UD...

everything appeared to work fine when bench testing my UD (using signal generator to simulate feedback) but the moment i connected the feedback CT nothing happened at the bridge

it took me a few hours to scope every gate and every IC on the board and when that returned no result the same amount of hours to read the UD documentation and redo the same measurements until i realized it was all because that pesky non inverting gate driver...

dexter, Fri Aug 18 2017, 09:09AM

Chris_Dickey wrote ...

The default state of the UCC27423 needs to be output high, in order to turn on the N-channel FET in the power stage.

See the schematic here, whose power stage is identical to the UD2.7. The reason I refer to this instead of the UD2.7 is that the internal schematic of an FDD8424H is shown on Steve's schematic, but hidden on Loneoceans'. (UD2.7 schematic is here, about halfway down the page.)

I'll go through this for the first gate driver, since all 4 are identical.

The reason for doing this is twofold:

1. The power stage itself (Q3A, Q3B) is both similar to a CMOS inverter (thus, high input -> low output) and...

2. The P-channel (high-side, Q3B) FET is AC-coupled.

Because of this, the P-channel FET can only be driven on for a short period of time (t << RC = 100nF * 1kΩ = 100µs); it must default to off (R22 discharges C26 and the gate capacitance of Q3B).

The UCC driver's (IC9A) output goes low when the enable pin goes low. This would try to drive the P-channel FET's (Q3B) gate low through a capacitor (C26). This would make it pulse low (turning the FET on), then decay to high (turning the FET off) due to R22, causing the power stage to go high-impedance. This is not something you want to do to because then nothing is controlling the gate voltage of the IGBTs in the bridge (via GDT2 connector -> GDT -> bridge IGBTs). Also, the pulse high, might turn the bridge on and leave it on when the output goes high-impedance.

If you had some sort of strange gate driver IC whose output was high when disabled, you could use the enable function of it directly. However, because most gate driver ICs with enable pins go low when disabled (including the UCC27423), the easier solution is to always have the UCC27423 driver enabled and to apply some logic gates to the inputs.

The default state of the UCC27423 needs to be output high, in order to turn on the N-channel FET in the power stage.

See the schematic here, whose power stage is identical to the UD2.7. The reason I refer to this instead of the UD2.7 is that the internal schematic of an FDD8424H is shown on Steve's schematic, but hidden on Loneoceans'. (UD2.7 schematic is here, about halfway down the page.)

I'll go through this for the first gate driver, since all 4 are identical.

The reason for doing this is twofold:

1. The power stage itself (Q3A, Q3B) is both similar to a CMOS inverter (thus, high input -> low output) and...

2. The P-channel (high-side, Q3B) FET is AC-coupled.

Because of this, the P-channel FET can only be driven on for a short period of time (t << RC = 100nF * 1kΩ = 100µs); it must default to off (R22 discharges C26 and the gate capacitance of Q3B).

The UCC driver's (IC9A) output goes low when the enable pin goes low. This would try to drive the P-channel FET's (Q3B) gate low through a capacitor (C26). This would make it pulse low (turning the FET on), then decay to high (turning the FET off) due to R22, causing the power stage to go high-impedance. This is not something you want to do to because then nothing is controlling the gate voltage of the IGBTs in the bridge (via GDT2 connector -> GDT -> bridge IGBTs). Also, the pulse high, might turn the bridge on and leave it on when the output goes high-impedance.

If you had some sort of strange gate driver IC whose output was high when disabled, you could use the enable function of it directly. However, because most gate driver ICs with enable pins go low when disabled (including the UCC27423), the easier solution is to always have the UCC27423 driver enabled and to apply some logic gates to the inputs.

for some odd reason i bought non inverting gate drive IS's for my UD...

everything appeared to work fine when bench testing my UD (using signal generator to simulate feedback) but the moment i connected the feedback CT nothing happened at the bridge

it took me a few hours to scope every gate and every IC on the board and when that returned no result the same amount of hours to read the UD documentation and redo the same measurements until i realized it was all because that pesky non inverting gate driver...

Print this page