Using PLLs for resonant tank control

Wolfram, Thu Oct 08 2015, 03:11PMAs I've been working with my induction heater project, I've played a lot with PLLs, and they have given me lots of trouble. This generally seems to match the experience of other members here as well. A few days ago, I started digging deeper into the problem and I discovered something very important. The usual XOR-type and edge triggered detectors are both inherently unsuitable for the control of resonant tank circuits, for different reasons. No wonder people have had trouble with them.

The simplest type of phase detector is the XOR type, often called "Type 1", consisting of a single XOR gate. This outputs a square wave with a duty cycle proportional to the phase difference. When this signal is filtered by a low pass filter, it gives a voltage that is proportional to the phase difference. This type of detector covers a range of 180 degrees. When the inputs are in phase, the output duty cycle is 0%, when the inputs are 180 degrees out of phase, the output duty cycle is 100%. Above 180 degrees, the duty cycle starts decreasing again, falling to 0% at 360 degrees.

The problem is that the phase in a resonant circuit swings through 180 degrees, and if the Q is high, this happens over a narrow frequency range. This is exactly the range covered by the phase detector, so it can be made to work. The problem comes when there is any additional phase shift, for example caused by delays in the IGBTs or the current sense transformer. If there is _any_ additional phase shift in the circuit, the phase will fall outside of the range of the detector and the output duty cycle will go in the opposite direction that it should. This will tell the VCO to increase the frequency when it should be decreased, and the VCO will go to the frequency limit and stick there. Here's a plot of what the transfer function will look like with 20 degrees of additional phase shift.

This is not guaranteed to happen in all cases, but it's likely to eventually show up. It took until the third revision of my induction heater before it showed up as a serious problem. That's the problem with marginal designs, they often work as they should then suddenly they don't. This can be generalized for all state-sensitive (combinatorial) phase detectors, any phase detector that only looks at the instantaneous value of the two inputs can only have a detection range of 180 degrees before the output wraps around.

The other common phase detector is the phase frequency detector. This type of phase detector looks at the edges of the two input signals. When the first edge comes, it starts charging or discharging the loop filter capacitor, and when the second edge comes, it stops. Whether it charges or discharges the capacitor depends on which edge comes first, if the edge from the VCO comes first, it starts discharging the loop filter capacitor. The result is that the VCO frequency is adjusted so that the edges come at the same time, that's the only way the VCO frequency is left at the same value.

The problem appears when this type of phase detector is used for sensing the tank phase, where both input frequencies are the same. If for example a glitch causes a false edge on the feedback input, the detector will loose track of which edge actually came first, and push the frequency in the wrong direction. I've illustrated this in the timing diagram above. The PLL will stay in this state, stuck at one of the ends of the range, until another glitch edge appears. What's even worse is, the PLL will often start up in this state and therefore never acquire lock in the first place. This problem was nicely described by Dr. Dark Current

.

.This situation can be generalized for all purely edge-triggered detectors. So where does that leave us? Both types of commonly used phase detectors are inherently unsuitable here. It turns out that there is a solution, and a very elegant one at that. A hybrid detector can be built which looks both at the edges and the states of the input. This type of detector can combine both the noise-immunity of the XOR type detector and the wide detection range of the edge sensitive detector. As an added bonus, this type of detector locks at zero degrees, so it can be used to lock series resonant tank current to the VCO frequency without any additional phase shifting tricks.

I have found this method documented in a paper [1], and a different, less elegant workaround is mentioned in an other paper by the same author [2]. Unfortunately, none of these are openly available on the web. I've therefore decided to document the method here. The detector is essentially the same as the edge sensitive detector, but the state machine is reset whenever the input signals are different. An even more elegant implementation is shown (without any further detail on the phase detector) in [3], and this is the one I've based my implementation on.

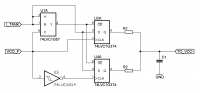

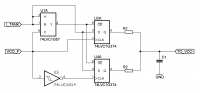

This implementation uses a D-flip flop to sample the feedback signal on the VCO clock edge, and uses this signal to select whether to increase or decrease the frequency. This gives it a +- 180 degree detection range. An XOR gate looks at the phase difference of the inputs, and applies the correction for the period that the signals are different by gating the output of the D-flip flop. Unfortunately, this type of phase detector can not be implemented from the phase detectors in the 4046 as we don't have access to some neccessary internal signals, but luckily it is easy to implement it with standard logic.

In my design I still chose to use the 4046 for its VCO and input amplifier, with the phase detector implemented with external logic. The design can be greatly simplified if a D-flip flop with output enable is used, and luckily these are available. I was able to implement the whole phase detector with two SOT23 devices at a total cost of under a dollar (about 25 cents in quantity 100). For fun, I made a quick 74HC4046-replacement with the new phase detector. It's pin compatible with the 74HC4046, but replaces the two phase comparators with the new one. I connected the new phase comparator output to both pin 2 and pin 13. This is a view of the underside of the board, where the components are mounted.

Note that I recently discovered this method, and I haven't yet received the parts to test it in practice, but the theory works out. I discussed these ideas with Steve Conner, and he's positive as well:

The stuff you told me over the last few days explains every weird anomaly I ever saw with my PLL drivers.

On a final note, I would highly recommend getting a copy of reference 3 for anybody interested in high frequency power electronics and especially Tesla coiling and induction heating. This paper contains a lot of very good information on high frequency resonant switching using IGBTs, and it presents a new method of power control. A prototype 100 kW 100 kHz IGBT inverter using 600 A bricks is presented, and they also do calorimetric efficiency measurements of different types of power control including phase shifting and detuning.

1: H. Karaca, "Phase detector for tuning circuit of resonant inverters",

Electronics Letters Vol. 36 No. 11, 25th May 2000

2: H. Karaca, "A malfunction problem and its solution in load resonant inverters ",

International Journal of Electronics, Volume 88, Issue 3, 2001

3: V. Esteve et al. "Enhanced Pulse-Density-Modulated Power Control for High Frequency Induction Heating Inverters",

IEEE Transactions on Industrial Electronics, Volume 62 Issue 11

Re: Using PLLs for resonant tank control

Steve Conner, Thu Oct 08 2015, 09:11PM

Excellent post! As I mentioned to Anders, when developing my PLL drivers, I noticed that the circuits using the type 1 phase detector sometimes failed to lock or got stuck, and the type 2 detector never worked for me at all. This post explains both problems nicely. Maybe it's time for a Mk3 PLL driver?

Steve Conner, Thu Oct 08 2015, 09:11PM

Excellent post! As I mentioned to Anders, when developing my PLL drivers, I noticed that the circuits using the type 1 phase detector sometimes failed to lock or got stuck, and the type 2 detector never worked for me at all. This post explains both problems nicely. Maybe it's time for a Mk3 PLL driver?

Re: Using PLLs for resonant tank control

Dago, Fri Oct 09 2015, 07:59AM

Interesting topic indeed!

I've been developing a fully digital induction heater driver and have run in to many many quite different approaches.

I've had an ARM-version working (not with an induction heater)

Then I kinda figured using an MCU can be a bit problematic and an FPGA would be an optimal solution. I've had a couple different sort of working (in simulation) models made with VHDL (example ) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

Currently been reading this paper and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

Dago, Fri Oct 09 2015, 07:59AM

Interesting topic indeed!

I've been developing a fully digital induction heater driver and have run in to many many quite different approaches.

I've had an ARM-version working (not with an induction heater)

Then I kinda figured using an MCU can be a bit problematic and an FPGA would be an optimal solution. I've had a couple different sort of working (in simulation) models made with VHDL (example

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.Currently been reading this paper

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?Re: Using PLLs for resonant tank control

Uspring, Fri Oct 09 2015, 01:16PM

Nice post

I've seen phase detectors, which I think are made of a 3 state machine, states 1, 2 and 3. One clock counts the state number up, the other one down. States 1 and 3 bias VCO voltage up and down, respectively. I believe, your circuit works similarly, although negative clock transition seem also to affect it.

By increasing the number of states, the catch range can be increased.

Uspring, Fri Oct 09 2015, 01:16PM

Nice post

I've seen phase detectors, which I think are made of a 3 state machine, states 1, 2 and 3. One clock counts the state number up, the other one down. States 1 and 3 bias VCO voltage up and down, respectively. I believe, your circuit works similarly, although negative clock transition seem also to affect it.

By increasing the number of states, the catch range can be increased.

Re: Using PLLs for resonant tank control

Wolfram, Fri Oct 09 2015, 04:51PM

Thanks.

Nice work. I am seriously considering migrating my own heater to an FPGA-based design at some point. Most of the conclusions from my first post apply to a PLL implemented digitally as well. Personally, I would make a phase accumulator oscillator, and just implement the loop integrator as a counter. The phase detector I described can be implemented directly in VHDL.

I don't have much time now, but I will try to get a chance to take a look at the paper over the weekend, but no guarantees. I find that if something is presented in a confusing way in a paper, it's often simpler to start from the basics and implement the idea from scratch using intuition.

Thanks.

This is the second type of phase detector I described. It works fine when trying to lock the VCO to an external input, but doesn't work well for resonant tank control as I described in my first post. In a PLL controlled induction heater or SSTC, both input signals come from the VCO but one is phase shifted through the tank circuit. This type of phase detector works fine as long as it starts up in the right state, but if a glitch causes it to enter the wrong state, it will not be able to recover and end up stuck to one end of the frequency range, the timing diagram in the first post shows this scenario.

Adding more states will not help in this case, the only result will be that there are more states that it won't be able to recover from.

Edit:

The new phase detector is actually simpler than it looks, I find it easiest to understand it as follows;

The VCO is running at some frequency and outputting a square wave signal. This signal is amplified by the H bridge and sent to the tank circuit. The current through the tank circuit is measured, and what we're interested in is the phase relation between this signal and the VCO signal. This phase relationship tells us if we are above or below Fres, in other words which way we need to adjust the VCO frequency. This phase shift is normally between +90 and -90 degrees, but this range can be shifted a bit due to delays in the H bridge and phase shifts in the current sensing network.

On the rising edge of the VCO clock, the D flip flop samples the feedback signal. If we are below Fres, the feedback signal (basically the sign of the current waveform) will be '1' at this time (the current is leading the voltage by 90 degrees so we're at the peak of the current waveform). This signal is kept by the D flip flop until the next rising edge of the VCO output. Now the D flip flop output is high, indicating that the frequency should be adjusted up. This signal is sent to the loop filter as long as the XOR output is high, i.e. as long as the inputs are different. This is a time period corresponding to the phase difference between the inputs. If the phase is close to 0 degrees, only narrow pulses of "correction" current are injected into the integrating capacitor, and if they are perfectly in phase then no change in frequency is made. The voltage on this capacitor controls the VCO frequency directly.

Wolfram, Fri Oct 09 2015, 04:51PM

Dago wrote ...

Interesting topic indeed!

I've been developing a fully digital induction heater driver and have run in to many many quite different approaches.

I've had an ARM-version working (not with an induction heater)

Then I kinda figured using an MCU can be a bit problematic and an FPGA would be an optimal solution. I've had a couple different sort of working (in simulation) models made with VHDL (example ) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

Currently been reading this paper and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

Interesting topic indeed!

I've been developing a fully digital induction heater driver and have run in to many many quite different approaches.

I've had an ARM-version working (not with an induction heater)

Then I kinda figured using an MCU can be a bit problematic and an FPGA would be an optimal solution. I've had a couple different sort of working (in simulation) models made with VHDL (example

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.

) but they both had some issues. That one has a phase-shift that is dependant on the frequency and I'd need a division to get rid of it and HW division is not nice. Then I made one version with a "type 2" PFD but so far have been unable to get it stable even though the filter should be fine and there should be phase margin.Currently been reading this paper

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?

and implementing it but I'm quite not 100% sure how am I supposed to handle the value coming from the "P2D". It is a signed number representing the phase error but how do I feed this to the filter... The output of the filter controls a "phase accumulator" which only takes in a positive number and changes the frequency accordingly. How should I scale the the signed number from the P2D for the filter? Should I add the number to the last value and keep it always positive? But that would be an integrator which would change the response right? Any suggestions?Thanks.

Nice work. I am seriously considering migrating my own heater to an FPGA-based design at some point. Most of the conclusions from my first post apply to a PLL implemented digitally as well. Personally, I would make a phase accumulator oscillator, and just implement the loop integrator as a counter. The phase detector I described can be implemented directly in VHDL.

I don't have much time now, but I will try to get a chance to take a look at the paper over the weekend, but no guarantees. I find that if something is presented in a confusing way in a paper, it's often simpler to start from the basics and implement the idea from scratch using intuition.

Nice post

I've seen phase detectors, which I think are made of a 3 state machine, states 1, 2 and 3. One clock counts the state number up, the other one down. States 1 and 3 bias VCO voltage up and down, respectively. I believe, your circuit works similarly, although negative clock transition seem also to affect it.

By increasing the number of states, the catch range can be increased.

Thanks.

This is the second type of phase detector I described. It works fine when trying to lock the VCO to an external input, but doesn't work well for resonant tank control as I described in my first post. In a PLL controlled induction heater or SSTC, both input signals come from the VCO but one is phase shifted through the tank circuit. This type of phase detector works fine as long as it starts up in the right state, but if a glitch causes it to enter the wrong state, it will not be able to recover and end up stuck to one end of the frequency range, the timing diagram in the first post shows this scenario.

Adding more states will not help in this case, the only result will be that there are more states that it won't be able to recover from.

Edit:

The new phase detector is actually simpler than it looks, I find it easiest to understand it as follows;

The VCO is running at some frequency and outputting a square wave signal. This signal is amplified by the H bridge and sent to the tank circuit. The current through the tank circuit is measured, and what we're interested in is the phase relation between this signal and the VCO signal. This phase relationship tells us if we are above or below Fres, in other words which way we need to adjust the VCO frequency. This phase shift is normally between +90 and -90 degrees, but this range can be shifted a bit due to delays in the H bridge and phase shifts in the current sensing network.

On the rising edge of the VCO clock, the D flip flop samples the feedback signal. If we are below Fres, the feedback signal (basically the sign of the current waveform) will be '1' at this time (the current is leading the voltage by 90 degrees so we're at the peak of the current waveform). This signal is kept by the D flip flop until the next rising edge of the VCO output. Now the D flip flop output is high, indicating that the frequency should be adjusted up. This signal is sent to the loop filter as long as the XOR output is high, i.e. as long as the inputs are different. This is a time period corresponding to the phase difference between the inputs. If the phase is close to 0 degrees, only narrow pulses of "correction" current are injected into the integrating capacitor, and if they are perfectly in phase then no change in frequency is made. The voltage on this capacitor controls the VCO frequency directly.

Re: Using PLLs for resonant tank control

BigBad, Sat Oct 10 2015, 05:53PM

If you know your frequency is between (say) 300-350khz then it it's possible to just use an arduino and undersample at (say) ~100khz frequencies. Once you've done that you can do much more complex PLL strategies, such as measuring the frequencies as well as the phase.

That will likely work extremely well unless the resonant frequency changes very quickly, I wouldn't have thought that that's a problem for induction heaters; but might be more problematic for Tesla coils where the resonance changes as it throws an arc.

BigBad, Sat Oct 10 2015, 05:53PM

If you know your frequency is between (say) 300-350khz then it it's possible to just use an arduino and undersample at (say) ~100khz frequencies. Once you've done that you can do much more complex PLL strategies, such as measuring the frequencies as well as the phase.

That will likely work extremely well unless the resonant frequency changes very quickly, I wouldn't have thought that that's a problem for induction heaters; but might be more problematic for Tesla coils where the resonance changes as it throws an arc.

Re: Using PLLs for resonant tank control

Uspring, Mon Oct 12 2015, 10:06AM

Wolfram, thank you for the explanation. I understand now, why the 3 state machine won't work.

I still don't understand your second diagram. It seems to indicate, that resonance is achieved at 50% XOR duty cycle. That corresponds to 90 degrees phase shift in your first diagram. In your last post you write:

Uspring, Mon Oct 12 2015, 10:06AM

Wolfram, thank you for the explanation. I understand now, why the 3 state machine won't work.

I still don't understand your second diagram. It seems to indicate, that resonance is achieved at 50% XOR duty cycle. That corresponds to 90 degrees phase shift in your first diagram. In your last post you write:

This phase relationship tells us if we are above or below Fres, in other words which way we need to adjust the VCO frequency. This phase shift is normally between +90 and -90 degrees...That seems to indicate, that resonance is at 0 degrees. Perhaps a minor point, but a XOR works best around 90 degrees and the the new circuit around 0 degrees.

Re: Using PLLs for resonant tank control

Wolfram, Mon Oct 12 2015, 06:21PM

This can work in theory but it will be difficult to get it working well in practice.

Your phase resolution will be inversely proportional to the difference between the VCO frequency and the closest integer multiple of the nyquist rate of your sampling frequency. For the induction heater, you want quite fine phase resolution, around the zero crossing even a few degrees can correspond to several amps of difference in switching current for the IGBTs. This means that you need to dynamically select the sampling frequency to be close to an integer fraction of your running frequency for acceptable performance. As you are undersampling, you're also very sensitive to sampling jitter, so you need to either sample using a hardware timer or do the code in assembly and count cycles.

I can't really think of any benefits of more complex PLL strategies. The purpose of the PLL is to find Fres and track it with an adjustable phase angle, and a plain analog PLL with my proposed phase detector does just that. Even if I had a microcontroller in my system, I would still strongly consider using the two 20 cent 74LVC1Gs.

Good point. I see that my original post was missing some information on this point. As the XOR phase detector transfer function has a reversal of the slope at zero degrees, it can't be used directly to lock tank current with bridge voltage. As the transfer function range is centered around 90 degrees, I introduced a 90 degree shift in my circuit to make the total phase shift 90 degrees at resonance. I did this by measuring tank cap voltage instead of tank current.

Wolfram, Mon Oct 12 2015, 06:21PM

BigBad wrote ...

If you know your frequency is between (say) 300-350khz then it it's possible to just use an arduino and undersample at (say) ~100khz frequencies. Once you've done that you can do much more complex PLL strategies, such as measuring the frequencies as well as the phase.

That will likely work extremely well unless the resonant frequency changes very quickly, I wouldn't have thought that that's a problem for induction heaters; but might be more problematic for Tesla coils where the resonance changes as it throws an arc.

If you know your frequency is between (say) 300-350khz then it it's possible to just use an arduino and undersample at (say) ~100khz frequencies. Once you've done that you can do much more complex PLL strategies, such as measuring the frequencies as well as the phase.

That will likely work extremely well unless the resonant frequency changes very quickly, I wouldn't have thought that that's a problem for induction heaters; but might be more problematic for Tesla coils where the resonance changes as it throws an arc.

This can work in theory but it will be difficult to get it working well in practice.

Your phase resolution will be inversely proportional to the difference between the VCO frequency and the closest integer multiple of the nyquist rate of your sampling frequency. For the induction heater, you want quite fine phase resolution, around the zero crossing even a few degrees can correspond to several amps of difference in switching current for the IGBTs. This means that you need to dynamically select the sampling frequency to be close to an integer fraction of your running frequency for acceptable performance. As you are undersampling, you're also very sensitive to sampling jitter, so you need to either sample using a hardware timer or do the code in assembly and count cycles.

I can't really think of any benefits of more complex PLL strategies. The purpose of the PLL is to find Fres and track it with an adjustable phase angle, and a plain analog PLL with my proposed phase detector does just that. Even if I had a microcontroller in my system, I would still strongly consider using the two 20 cent 74LVC1Gs.

Uspring wrote ...

Wolfram, thank you for the explanation. I understand now, why the 3 state machine won't work.

I still don't understand your second diagram. It seems to indicate, that resonance is achieved at 50% XOR duty cycle. That corresponds to 90 degrees phase shift in your first diagram. In your last post you write:

Wolfram, thank you for the explanation. I understand now, why the 3 state machine won't work.

I still don't understand your second diagram. It seems to indicate, that resonance is achieved at 50% XOR duty cycle. That corresponds to 90 degrees phase shift in your first diagram. In your last post you write:

This phase relationship tells us if we are above or below Fres, in other words which way we need to adjust the VCO frequency. This phase shift is normally between +90 and -90 degrees...That seems to indicate, that resonance is at 0 degrees. Perhaps a minor point, but a XOR works best around 90 degrees and the the new circuit around 0 degrees.

Good point. I see that my original post was missing some information on this point. As the XOR phase detector transfer function has a reversal of the slope at zero degrees, it can't be used directly to lock tank current with bridge voltage. As the transfer function range is centered around 90 degrees, I introduced a 90 degree shift in my circuit to make the total phase shift 90 degrees at resonance. I did this by measuring tank cap voltage instead of tank current.

Re: Using PLLs for resonant tank control

Carbon_Rod, Mon Oct 12 2015, 09:15PM

@BigBad

In general, the commercial driver circuits can include a number of design specific safeguards to try and mitigate issues with saturation and dynamic changes in the inductor during use. However, these can still fail given soft-starting the driver may not work if the initial inrush exceeds the coils rating plus the ripple current. Current regulation/monitoring may also be insufficient if the driver essentially experiences a fold-over prior to the feedback system tripping a limit. Additionally, the tolerances of both L & C components may drift around in non-linear ways, and even expensive switching output sections recommend a minimum 30% margin for SOA (realistically one can expect 20% for ceramic dialectic C, and 10% to 30% for L). Also, it may be counter intuitive to consider that an output section with ultra-fast freewheeling diodes may cause transients in the output section that can certainly damage the drivers.

However, adjusting the dwell times in the switching section could certainly be an advantage, as regulating the driver duty cycle at a specific frequency could avoid saturation related failures. Indeed, this is how most type III based regulators are intended to work.

Carbon_Rod, Mon Oct 12 2015, 09:15PM

@BigBad

In general, the commercial driver circuits can include a number of design specific safeguards to try and mitigate issues with saturation and dynamic changes in the inductor during use. However, these can still fail given soft-starting the driver may not work if the initial inrush exceeds the coils rating plus the ripple current. Current regulation/monitoring may also be insufficient if the driver essentially experiences a fold-over prior to the feedback system tripping a limit. Additionally, the tolerances of both L & C components may drift around in non-linear ways, and even expensive switching output sections recommend a minimum 30% margin for SOA (realistically one can expect 20% for ceramic dialectic C, and 10% to 30% for L). Also, it may be counter intuitive to consider that an output section with ultra-fast freewheeling diodes may cause transients in the output section that can certainly damage the drivers.

However, adjusting the dwell times in the switching section could certainly be an advantage, as regulating the driver duty cycle at a specific frequency could avoid saturation related failures. Indeed, this is how most type III based regulators are intended to work.

Re: Using PLLs for resonant tank control

Uspring, Tue Oct 13 2015, 09:04AM

An idea:

The FF in the new circuit determines which positive transition comes early. It is enabled as long as input signals are different. The phase detection speed can be doubled by adding the voltage from a similar circuit responsive to negative transitions. For the rapidly changing phases in a TC that might be an advantage.

Uspring, Tue Oct 13 2015, 09:04AM

An idea:

The FF in the new circuit determines which positive transition comes early. It is enabled as long as input signals are different. The phase detection speed can be doubled by adding the voltage from a similar circuit responsive to negative transitions. For the rapidly changing phases in a TC that might be an advantage.

Re: Using PLLs for resonant tank control

Dago, Wed Oct 14 2015, 01:57PM

I made an ADPLL implementation in VHDL based on the phase-detector Wolfram had found and detailed in the OP: I have included ModelSim project files, waveform setup scripts and simple test benches for the components.

I have included ModelSim project files, waveform setup scripts and simple test benches for the components.

The ADPLL consists of the phase-detector, a time-to-digital converter (essentially a counter that gives off a signed value of the phase difference between signal and reference), a filter (very simple first order RC-filter with bit shifts) and a phase accumulator as the oscillator. Unfortunately the ADPLL does not quite work yet, with the attached test bench it is stable for a while before it starts to oscillate: I tried playing around with the filter parameters but didn't manage to get it stable yet. I calculated the parameters based on the paper I linked in an earlier post but it was not stable with those parameters either. I have a feeling there is some bug/fundamental problem with it that I am not yet seeing :)

I tried playing around with the filter parameters but didn't manage to get it stable yet. I calculated the parameters based on the paper I linked in an earlier post but it was not stable with those parameters either. I have a feeling there is some bug/fundamental problem with it that I am not yet seeing :)

I have a fancier second order IIR filter implemented with fixed point arithmetics but I am not quite sure how to properly calculate the coefficients.

One fundamental question: Should the filter behave as if the input value is a current or a voltage? Ie. if I set a fixed input value should the output value approach it linearly or logarithmically? The filter outlined in the paper approaches it linearly and my IIR implementation logarithmically.

Dago, Wed Oct 14 2015, 01:57PM

I made an ADPLL implementation in VHDL based on the phase-detector Wolfram had found and detailed in the OP:

I have included ModelSim project files, waveform setup scripts and simple test benches for the components.

I have included ModelSim project files, waveform setup scripts and simple test benches for the components.The ADPLL consists of the phase-detector, a time-to-digital converter (essentially a counter that gives off a signed value of the phase difference between signal and reference), a filter (very simple first order RC-filter with bit shifts) and a phase accumulator as the oscillator. Unfortunately the ADPLL does not quite work yet, with the attached test bench it is stable for a while before it starts to oscillate:

I tried playing around with the filter parameters but didn't manage to get it stable yet. I calculated the parameters based on the paper I linked in an earlier post but it was not stable with those parameters either. I have a feeling there is some bug/fundamental problem with it that I am not yet seeing :)

I tried playing around with the filter parameters but didn't manage to get it stable yet. I calculated the parameters based on the paper I linked in an earlier post but it was not stable with those parameters either. I have a feeling there is some bug/fundamental problem with it that I am not yet seeing :)I have a fancier second order IIR filter implemented with fixed point arithmetics but I am not quite sure how to properly calculate the coefficients.

One fundamental question: Should the filter behave as if the input value is a current or a voltage? Ie. if I set a fixed input value should the output value approach it linearly or logarithmically? The filter outlined in the paper approaches it linearly and my IIR implementation logarithmically.

Re: Using PLLs for resonant tank control

Dago, Sun Oct 18 2015, 01:24PM

I managed to get my VHDL-implementation working. I have uploaded all of my VHDL to GitHub:

Dago, Sun Oct 18 2015, 01:24PM

I managed to get my VHDL-implementation working. I have uploaded all of my VHDL to GitHub:

Re: Using PLLs for resonant tank control

parasole, Tue Nov 24 2015, 08:56AM

Interesting topic, then I broaden my search and found that there is ADPLL IC available from TI: 74ls297

If you do a search for this IC than you will get quite a number of interesting results and one being VHDL implementation of this IC...

parasole, Tue Nov 24 2015, 08:56AM

Interesting topic, then I broaden my search and found that there is ADPLL IC available from TI: 74ls297

If you do a search for this IC than you will get quite a number of interesting results and one being VHDL implementation of this IC...

Re: Using PLLs for resonant tank control

Wolfram, Sun Dec 20 2015, 10:44PM

I forgot to update this thread with actual test results. I implemented this phase detector in my heater prototype, and I've verified that it works as well as expected. Initially I had some trouble getting a stable phase lock, but this turned out to be caused by problems in my primary current phase measurement circuit. My circuit had the CT loaded by diodes, and their significant and non-linear capacitance introduced current-dependant phase shifts and duty cycle variations that resulted in erratic behavior. Once I fixed the current phase sensing, the circuit started working correctly. It acquires lock at very low DC bus voltages, and it maintains lock through the whole mains period with unsmoothed rectified mains on the DC bus.

I attempted to adjust the switching phase angle by injecting a DC current into the loop filter capacitor node, but I never got this to work right. Instead, I implemented switching phase control by adding a delay circuit between the VCO output and the phase detector input. By adjusting this delay, I can adjust how early or late the IGBTs will switch in relation to current zero crossing.

Uspring: The idea with updating the flip-flop on both clock edges is brilliant! Especially as you suggest for TCs and other applications with rapid phase changes. It takes some more logic to implement, but this is no problem if it is done in an FPGA.

Dago: Nice implementation! This will save me some work when I migrate my project to an FPGA some time in the future.

Wolfram, Sun Dec 20 2015, 10:44PM

I forgot to update this thread with actual test results. I implemented this phase detector in my heater prototype, and I've verified that it works as well as expected. Initially I had some trouble getting a stable phase lock, but this turned out to be caused by problems in my primary current phase measurement circuit. My circuit had the CT loaded by diodes, and their significant and non-linear capacitance introduced current-dependant phase shifts and duty cycle variations that resulted in erratic behavior. Once I fixed the current phase sensing, the circuit started working correctly. It acquires lock at very low DC bus voltages, and it maintains lock through the whole mains period with unsmoothed rectified mains on the DC bus.

I attempted to adjust the switching phase angle by injecting a DC current into the loop filter capacitor node, but I never got this to work right. Instead, I implemented switching phase control by adding a delay circuit between the VCO output and the phase detector input. By adjusting this delay, I can adjust how early or late the IGBTs will switch in relation to current zero crossing.

Uspring: The idea with updating the flip-flop on both clock edges is brilliant! Especially as you suggest for TCs and other applications with rapid phase changes. It takes some more logic to implement, but this is no problem if it is done in an FPGA.

Dago: Nice implementation! This will save me some work when I migrate my project to an FPGA some time in the future.

Re: Using PLLs for resonant tank control

parasole, Mon Dec 21 2015, 07:51PM

I did some play around Dago code (thanks for it!) and came up with lighter version which could be used with additional controller (cheap AVR) for service functions. The core part came up with only 331 LE which is fitting nicely in cheap CPLD device (EPM570 in my example). Another microcontroller could be used for temperature control (the function which I excluded from CPLD since it requires lot of resources), PDM modulation level setting (rotary encoder as input to the controller) as well as different measurements like currents, working frequency and so one.

parasole, Mon Dec 21 2015, 07:51PM

I did some play around Dago code (thanks for it!) and came up with lighter version which could be used with additional controller (cheap AVR) for service functions. The core part came up with only 331 LE which is fitting nicely in cheap CPLD device (EPM570 in my example). Another microcontroller could be used for temperature control (the function which I excluded from CPLD since it requires lot of resources), PDM modulation level setting (rotary encoder as input to the controller) as well as different measurements like currents, working frequency and so one.

Re: Using PLLs for resonant tank control

parasole, Mon Jan 11 2016, 05:10PM

Further exploring ADPLL topic, I found interesting paper with an alternative solution for ADPLL, the idea is to change the tracking step, with narrow one and precise while in sync and widening when sync is acquired...

I did implement M_change module as I understood it, it looks to be working in the sim, however not fully sure about how well it is done. Any one more proficient in vhdl and want to have a look let me know about...

]fpga-based_induction_heating_adpll.pdf[/file]

parasole, Mon Jan 11 2016, 05:10PM

Further exploring ADPLL topic, I found interesting paper with an alternative solution for ADPLL, the idea is to change the tracking step, with narrow one and precise while in sync and widening when sync is acquired...

I did implement M_change module as I understood it, it looks to be working in the sim, however not fully sure about how well it is done. Any one more proficient in vhdl and want to have a look let me know about...

]fpga-based_induction_heating_adpll.pdf[/file]

Re: Using PLLs for resonant tank control

Sigurthr, Mon Jan 11 2016, 05:46PM

I'm just now seeing this thread, excellent work Wolfram et al. I've commented on the shortcomings of the 4046 in SSTC applications a lot over the years but never had any solution or hard data on what causes the problems. Thank you for clearing both up! Out of six PLL coils I only ever got one to work right, and I've damned near framed the driver, haha.

Any chance at a schematic for this modified solution for TC use? I'd love to try implementing this fix in the future. Any application notes you can add would be appreciated, especially since you had to revise your tank sense circuitry.

Sigurthr, Mon Jan 11 2016, 05:46PM

Wolfram wrote ...

Uspring: The idea with updating the flip-flop on both clock edges is brilliant! Especially as you suggest for TCs and other applications with rapid phase changes. It takes some more logic to implement, but this is no problem if it is done in an FPGA.

Uspring: The idea with updating the flip-flop on both clock edges is brilliant! Especially as you suggest for TCs and other applications with rapid phase changes. It takes some more logic to implement, but this is no problem if it is done in an FPGA.

I'm just now seeing this thread, excellent work Wolfram et al. I've commented on the shortcomings of the 4046 in SSTC applications a lot over the years but never had any solution or hard data on what causes the problems. Thank you for clearing both up! Out of six PLL coils I only ever got one to work right, and I've damned near framed the driver, haha.

Any chance at a schematic for this modified solution for TC use? I'd love to try implementing this fix in the future. Any application notes you can add would be appreciated, especially since you had to revise your tank sense circuitry.

Re: Using PLLs for resonant tank control

Uspring, Wed Jan 13 2016, 02:19PM

Sigurthr wrote:

In the first circuit, you input VCO_F and I_TANK and in the other one the inverted versions of these signals. You the average the outputs, e.g. by connecting the second circuits Q with an extra R3 to C1.

Uspring, Wed Jan 13 2016, 02:19PM

Sigurthr wrote:

Any chance at a schematic for this modified solution for TC use?You need 2 copies of Wolframs circuit:

In the first circuit, you input VCO_F and I_TANK and in the other one the inverted versions of these signals. You the average the outputs, e.g. by connecting the second circuits Q with an extra R3 to C1.

Re: Using PLLs for resonant tank control

Wolfram, Wed Jan 13 2016, 03:58PM

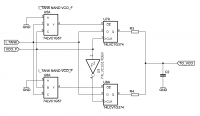

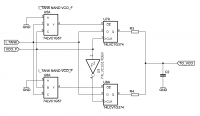

It is possible to simplify the circuit a bit further without changing its operation. An XOR with the inputs inverted is identical to a regular XOR, so you don't have to duplicate this part. This also saves an inverter, since you only need to invert the reference phase input for the second phase detector.

This solution might not be as fast as it could be, whenever one flip flop is updated with the latest sampled value, the other one will still be driving the loop filter with the previous sampled value. I guess this is gives it a pole in the Z plane.

This can be solved with just a tiny bit more logic. Decomposing the XOR function into two separate gates allows us to enable each D-FF only on its the half-cycle that it sampled. In both these circuits, the 74LVC1G14 can be replaced by a 74LVC1G57 if you want to minimize the number of different chips in the design. The logic can of course also be implemented in any technology where the neccessary logic is available. Also note that these double-edge phase detector designs are untested as of now.

The speed advantage over the single edge phase detector is only worth the added complexity in cases where where the phase can change significantly from one half cycle to the next. A typical case is in a DRSSTC. I don't know if the dual-edge loop filter has an advantage over the single-edge one in a typical SSTC. In an induction heater the benefit is insignificant, wo I will be sticking to the single-edge one for now.

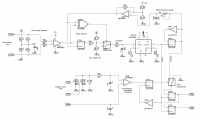

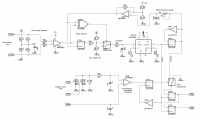

Lastly, I've attached a schematic of the PLL/PDM core in the latest revision of my induction heater. This shows another implementation of the single-edge resonant phase detector, using the XOR PD in the 4046. Here you can see the improved current sign detector and the fully synchronous enable logic as well.

Wolfram, Wed Jan 13 2016, 03:58PM

Uspring wrote ...

Sigurthr wrote:

In the first circuit, you input VCO_F and I_TANK and in the other one the inverted versions of these signals. You the average the outputs, e.g. by connecting the second circuits Q with an extra R3 to C1.

Sigurthr wrote:

Any chance at a schematic for this modified solution for TC use?You need 2 copies of Wolframs circuit:

In the first circuit, you input VCO_F and I_TANK and in the other one the inverted versions of these signals. You the average the outputs, e.g. by connecting the second circuits Q with an extra R3 to C1.

It is possible to simplify the circuit a bit further without changing its operation. An XOR with the inputs inverted is identical to a regular XOR, so you don't have to duplicate this part. This also saves an inverter, since you only need to invert the reference phase input for the second phase detector.

This solution might not be as fast as it could be, whenever one flip flop is updated with the latest sampled value, the other one will still be driving the loop filter with the previous sampled value. I guess this is gives it a pole in the Z plane.

This can be solved with just a tiny bit more logic. Decomposing the XOR function into two separate gates allows us to enable each D-FF only on its the half-cycle that it sampled. In both these circuits, the 74LVC1G14 can be replaced by a 74LVC1G57 if you want to minimize the number of different chips in the design. The logic can of course also be implemented in any technology where the neccessary logic is available. Also note that these double-edge phase detector designs are untested as of now.

The speed advantage over the single edge phase detector is only worth the added complexity in cases where where the phase can change significantly from one half cycle to the next. A typical case is in a DRSSTC. I don't know if the dual-edge loop filter has an advantage over the single-edge one in a typical SSTC. In an induction heater the benefit is insignificant, wo I will be sticking to the single-edge one for now.

Lastly, I've attached a schematic of the PLL/PDM core in the latest revision of my induction heater. This shows another implementation of the single-edge resonant phase detector, using the XOR PD in the 4046. Here you can see the improved current sign detector and the fully synchronous enable logic as well.

Re: Using PLLs for resonant tank control

Uspring, Thu Jan 14 2016, 11:00AM

Uspring, Thu Jan 14 2016, 11:00AM

This solution might not be as fast as it could be, whenever one flip flop is updated with the latest sampled value, the other one will still be driving the loop filter with the previous sampled value.Yes, a nice circuit modification. For fastest response one also needs to take into account, that a simple RC low pass filter involves long term memory of previous phases. That can be seen by its representation as a convolution integral in the time domain. Better filters seem possible. For optimisation freaks an endless topic

Re: Using PLLs for resonant tank control

Durchgebaut, Fri May 27 2016, 09:20PM

Your first PLL circuit looks very promising, I got your first schematic working in the Falstad's Circuit Simulator.

Maybe someone can use this simulation to easier understand how this circuit works.

How should I get started making a digital PLL for an induction heater? Is it possible to recreate the whole circuit from Wolfram in code for a microcontroller?

Durchgebaut, Fri May 27 2016, 09:20PM

Your first PLL circuit looks very promising, I got your first schematic working in the Falstad's Circuit Simulator.

Maybe someone can use this simulation to easier understand how this circuit works.

How should I get started making a digital PLL for an induction heater? Is it possible to recreate the whole circuit from Wolfram in code for a microcontroller?

Print this page