First SSTC design - Need some critique

DerStrom8, Wed Jun 25 2014, 08:45PMNOTE: After working more on this project, I have decided to build a DRSSTC, rather than a standard SSTC as I originally planned. Many of my earlier posts no longer apply.

Hi folks,

I joined some time ago but dropped off the map for a bit. Now I'm back for a little assistance.

I recently got around to starting my own DRSSTC design, though to be honest I have no idea what I'm doing--I'm learning as I go. I have drawn out a basic circuit utilizing the TC4420/9 MOSFET drivers (one non-inverting, and one inverting) and a full H-bridge to drive the primary. A 1:50 transformer on the secondary passes a feedback signal through some cleanup circuitry (two Schmitt-trigger inverters) back into the 4420/9.

I have little no doubt there is a fair amount that I missed, or that is calculated incorrectly, but I figured if anyone could look it over and critique it, it would be you folks.

The circuit is only in the design stage, so a lot of the part numbers (FETs, especially) are not the actual components I will be using. I only used them in the circuit to get the simulation to work, since PROTEUS did not have all of the components I planned to use. So I guess just consider them symbolically and don't pay much attention to the actual part numbers.

Any help would be greatly appreciated. As I said, this is entirely new to me and I am continuously trying to learn. Let me know if you would also like the Proteus design files for simulation.

Thanks folks!

Regards,

Matt

Re: First SSTC design - Need some critique

Sigurthr, Thu Jun 26 2014, 12:43AM

Your high side fets are lacking a return current path for the gate drive signal. When the low side left fet is off there's no connection between the high side left Source and ground except through the primary and the low side right fet. Abandon the center tapped GDT and run a standard pentafiliar 1:1:1:1:1 GDT.

I'm not sure what you're doing with TR1 and TR2, but you left out the actual TC primary (unless one of those is meant to be coreless). Just use a single current transformer for feedback on the primary circuit, and don't ground any side of the primary circuit. What you have there looks more like you're trying to impedance match the inverter to the load, but that's only needed when running an inverter away from resonance, which you won't be doing.

Sigurthr, Thu Jun 26 2014, 12:43AM

Your high side fets are lacking a return current path for the gate drive signal. When the low side left fet is off there's no connection between the high side left Source and ground except through the primary and the low side right fet. Abandon the center tapped GDT and run a standard pentafiliar 1:1:1:1:1 GDT.

I'm not sure what you're doing with TR1 and TR2, but you left out the actual TC primary (unless one of those is meant to be coreless). Just use a single current transformer for feedback on the primary circuit, and don't ground any side of the primary circuit. What you have there looks more like you're trying to impedance match the inverter to the load, but that's only needed when running an inverter away from resonance, which you won't be doing.

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 01:35AM

Hi Sigurthr, thanks for the response.

I just realized I posted the wrong schematic. I've re-attached it, this time with the correct one.

TR1, as shown in the notes, is the primary/secondary. It should be coreless but I am not sure how to create coreless transformers for use in Proteus. I should have mentioned that in my original post. I am using a cored transformer just for the sake of simulation, and it does not reflect the actual circuit I will be using.

TR2 is the feedback transformer, which consists of 1 turn of the secondary and 50 turns going to the feedback cleanup circuitry.

I'm not sure what you're referring to when you say there's no return path for the gate drive signal. The GDT is grounded on the center tap, and the "bottom" of the H-bridge is also grounded. Was thinking that would serve as the return? When the left FET is off, then so is the low-side right FET, and the high-side right and low-side left FETs are on, feeding current through the Primary.

That's a good idea using the 1:1:1:1:1 though. I am assuming that is one winding for the TC4420/9, and one for each FET, am I correct?

Much obliged!

Matt

DerStrom8, Thu Jun 26 2014, 01:35AM

Sigurthr wrote ...

Your high side fets are lacking a return current path for the gate drive signal. When the low side left fet is off there's no connection between the high side left Source and ground except through the primary and the low side right fet. Abandon the center tapped GDT and run a standard pentafiliar 1:1:1:1:1 GDT.

I'm not sure what you're doing with TR1 and TR2, but you left out the actual TC primary (unless one of those is meant to be coreless). Just use a single current transformer for feedback on the primary circuit, and don't ground any side of the primary circuit. What you have there looks more like you're trying to impedance match the inverter to the load, but that's only needed when running an inverter away from resonance, which you won't be doing.

Your high side fets are lacking a return current path for the gate drive signal. When the low side left fet is off there's no connection between the high side left Source and ground except through the primary and the low side right fet. Abandon the center tapped GDT and run a standard pentafiliar 1:1:1:1:1 GDT.

I'm not sure what you're doing with TR1 and TR2, but you left out the actual TC primary (unless one of those is meant to be coreless). Just use a single current transformer for feedback on the primary circuit, and don't ground any side of the primary circuit. What you have there looks more like you're trying to impedance match the inverter to the load, but that's only needed when running an inverter away from resonance, which you won't be doing.

Hi Sigurthr, thanks for the response.

I just realized I posted the wrong schematic. I've re-attached it, this time with the correct one.

TR1, as shown in the notes, is the primary/secondary. It should be coreless but I am not sure how to create coreless transformers for use in Proteus. I should have mentioned that in my original post. I am using a cored transformer just for the sake of simulation, and it does not reflect the actual circuit I will be using.

TR2 is the feedback transformer, which consists of 1 turn of the secondary and 50 turns going to the feedback cleanup circuitry.

I'm not sure what you're referring to when you say there's no return path for the gate drive signal. The GDT is grounded on the center tap, and the "bottom" of the H-bridge is also grounded. Was thinking that would serve as the return? When the left FET is off, then so is the low-side right FET, and the high-side right and low-side left FETs are on, feeding current through the Primary.

That's a good idea using the 1:1:1:1:1 though. I am assuming that is one winding for the TC4420/9, and one for each FET, am I correct?

Much obliged!

Matt

Re: First SSTC design - Need some critique

Sigurthr, Thu Jun 26 2014, 04:37AM

Yep, in pentafiliar one is for the primary, and four secondaries - one for each fet. This balances inductances and interwinding capacitances evenly.

The Gate-Source current of Q1 has to flow through the primary and then through DS junction of Q3 in order to return to the grounded center tap of the GDT. The same goes for Q4 and Q2. The problem is that this means that Q1 cannot turn on until Q3 has turned on, and the time Q3 spends in the linear state causes Q1 to spend an even longer time in the linear state. Not to mention the additional impedances presented to the gate drive current from having to flow through the primary which will likely greatly distort the gate signals. The result is instead of switching on as Q1/Q3 then Q2/Q4 you get Q3 then Q1 then Q2 then Q4. This greatly magnifies losses and presents a huge cross conduction hazard.

Also, you need a DC blocking capacitor on the primary of the GDT or else the GDT will appear as a short to the gate drive chips, blowing them up.

My instinct says that grounding the center tap of the GDT also causes you to present the full voltage differential between the positive rail of the Bus and ground to the Gate-Source junction, which will surely destroy the fets. It is late and I'm getting a bit fuzzy doing the simulation of this running in my head so take this last part with a grain of salt, but it doesn't look viable to me.

Sigurthr, Thu Jun 26 2014, 04:37AM

Yep, in pentafiliar one is for the primary, and four secondaries - one for each fet. This balances inductances and interwinding capacitances evenly.

The Gate-Source current of Q1 has to flow through the primary and then through DS junction of Q3 in order to return to the grounded center tap of the GDT. The same goes for Q4 and Q2. The problem is that this means that Q1 cannot turn on until Q3 has turned on, and the time Q3 spends in the linear state causes Q1 to spend an even longer time in the linear state. Not to mention the additional impedances presented to the gate drive current from having to flow through the primary which will likely greatly distort the gate signals. The result is instead of switching on as Q1/Q3 then Q2/Q4 you get Q3 then Q1 then Q2 then Q4. This greatly magnifies losses and presents a huge cross conduction hazard.

Also, you need a DC blocking capacitor on the primary of the GDT or else the GDT will appear as a short to the gate drive chips, blowing them up.

My instinct says that grounding the center tap of the GDT also causes you to present the full voltage differential between the positive rail of the Bus and ground to the Gate-Source junction, which will surely destroy the fets. It is late and I'm getting a bit fuzzy doing the simulation of this running in my head so take this last part with a grain of salt, but it doesn't look viable to me.

Re: First SSTC design - Need some critique

GrantX, Thu Jun 26 2014, 06:28AM

I believe this is correct. The voltage you need to apply to the gates is relative to the SOURCE of the MOSFET. If the inverter is running off rectified 230V then the source of the high side transistors will be way over a hundred volts away from ground - so your grounded GDT will cause the gates to be annihilated instantly (and a lot of fault current will flow through the GDT and dead transistors - flames and booms). With isolated GDT windings, you connect the "bottom" of the coil (remembering correct phasing) directly to the source pin of the transistor that winding is driving. Then the "top" of that coil connects to the gate through the appropriate-sized gate resistor. Now the gate voltage is relative to the source of the FET - even if it's floating at several hundred volts the gate will only see the +/- 12-20 volt (whatever you choose) produced by the GDT. It's a good idea to use wire with decent insulation in your GDT, since it will be experiencing a couple of hundred volts. Its also a good idea to use "back to back" zeners across the gate and source pins to protect the gates from any unwanted spikes.

At least, that's what I'm seeing right now, if I'm wrong hopefully someone will point it out :)

GrantX, Thu Jun 26 2014, 06:28AM

Sigurthr wrote ...

Yep, in pentafiliar one is for the primary, and four secondaries - one for each fet. This balances inductances and interwinding capacitances evenly.

My instinct says that grounding the center tap of the GDT also causes you to present the full voltage differential between the positive rail of the Bus and ground to the Gate-Source junction, which will surely destroy the fets. It is late and I'm getting a bit fuzzy doing the simulation of this running in my head so take this last part with a grain of salt, but it doesn't look viable to me.

Yep, in pentafiliar one is for the primary, and four secondaries - one for each fet. This balances inductances and interwinding capacitances evenly.

My instinct says that grounding the center tap of the GDT also causes you to present the full voltage differential between the positive rail of the Bus and ground to the Gate-Source junction, which will surely destroy the fets. It is late and I'm getting a bit fuzzy doing the simulation of this running in my head so take this last part with a grain of salt, but it doesn't look viable to me.

I believe this is correct. The voltage you need to apply to the gates is relative to the SOURCE of the MOSFET. If the inverter is running off rectified 230V then the source of the high side transistors will be way over a hundred volts away from ground - so your grounded GDT will cause the gates to be annihilated instantly (and a lot of fault current will flow through the GDT and dead transistors - flames and booms). With isolated GDT windings, you connect the "bottom" of the coil (remembering correct phasing) directly to the source pin of the transistor that winding is driving. Then the "top" of that coil connects to the gate through the appropriate-sized gate resistor. Now the gate voltage is relative to the source of the FET - even if it's floating at several hundred volts the gate will only see the +/- 12-20 volt (whatever you choose) produced by the GDT. It's a good idea to use wire with decent insulation in your GDT, since it will be experiencing a couple of hundred volts. Its also a good idea to use "back to back" zeners across the gate and source pins to protect the gates from any unwanted spikes.

At least, that's what I'm seeing right now, if I'm wrong hopefully someone will point it out :)

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 11:53AM

Hello, I'm afraid you still don't understand basics of electronics (there are really a lot of flaws in your circuit), I don't mean this in an offensive way but I think you should really follow a tried design for your first coil, like the Mini SSTC by Steve Ward.

Dr. Dark Current, Thu Jun 26 2014, 11:53AM

Hello, I'm afraid you still don't understand basics of electronics (there are really a lot of flaws in your circuit), I don't mean this in an offensive way but I think you should really follow a tried design for your first coil, like the Mini SSTC by Steve Ward.

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 12:55PM

Hi Everyone,

This is a lot of great feedback, thank you very much! It looks like I'll definitely have to re-think a lot of my circuit, so I'll keep this in mind when redrawing it.

I'll post back when I have something more.

@Dr. Dark Current--

The point of this project is not simply to build a SSTC. It's to learn how to design one. The design process is the most important part, so simply taking someone else's design really doesn't interest me. And for the record, I understand the basics of electronics, but SSTCs have a lot going on at once and my brain often can't keep up :p

Thanks for the information guys!

DerStrom8, Thu Jun 26 2014, 12:55PM

Hi Everyone,

This is a lot of great feedback, thank you very much! It looks like I'll definitely have to re-think a lot of my circuit, so I'll keep this in mind when redrawing it.

I'll post back when I have something more.

@Dr. Dark Current--

The point of this project is not simply to build a SSTC. It's to learn how to design one. The design process is the most important part, so simply taking someone else's design really doesn't interest me. And for the record, I understand the basics of electronics, but SSTCs have a lot going on at once and my brain often can't keep up :p

Thanks for the information guys!

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 04:32PM

I think the best way to get started is to build a proven design and then learn from it. I'd say this is the quickiest way to learn and then you'll be able to design a much better circuit.

But anyway:

-Pulling the gate drivers' inputs low or high during OFF-time is wrong, you must make sure that both drivers outputs are LOW or both HIGH during the OFF-time. Use the ENABLE pins of G-drivers or NAND gates.

-The GDT connection is horribly wrong. Just look at any other SSTC design, they all use similar connection of GDT secondaries.

-The GDT should have a 1:1 turns ratio. Wind it by insulated wires twisted together (eg. wires from an UTP cable) to form a "stranded wire". This way you'll get the lowest leakage inductance.

-Connect a 1-10uF ceramic/film cap in series with GDT primary to block DC voltage.

-Remove the resistor on CT output and replace it with a ~10nF capacitor to block DC voltage. The zener diode has a too high capacitance and it will increase your loop delay; use two 1N4148 diodes to clamp the CT output to the zener diode (to decrease capacitances).

-Gate driver decoupling caps are not drawn but I suppose you'll use them.

-The bridge is missing its decoupling capacitor as well.

-If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

Dr. Dark Current, Thu Jun 26 2014, 04:32PM

I think the best way to get started is to build a proven design and then learn from it. I'd say this is the quickiest way to learn and then you'll be able to design a much better circuit.

But anyway:

-Pulling the gate drivers' inputs low or high during OFF-time is wrong, you must make sure that both drivers outputs are LOW or both HIGH during the OFF-time. Use the ENABLE pins of G-drivers or NAND gates.

-The GDT connection is horribly wrong. Just look at any other SSTC design, they all use similar connection of GDT secondaries.

-The GDT should have a 1:1 turns ratio. Wind it by insulated wires twisted together (eg. wires from an UTP cable) to form a "stranded wire". This way you'll get the lowest leakage inductance.

-Connect a 1-10uF ceramic/film cap in series with GDT primary to block DC voltage.

-Remove the resistor on CT output and replace it with a ~10nF capacitor to block DC voltage. The zener diode has a too high capacitance and it will increase your loop delay; use two 1N4148 diodes to clamp the CT output to the zener diode (to decrease capacitances).

-Gate driver decoupling caps are not drawn but I suppose you'll use them.

-The bridge is missing its decoupling capacitor as well.

-If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 05:09PM

Excellent comments, Dr. Dark Current, thank you. This is why I came here--for replies like yours!

The other issue I didn't mention was that I am limited for parts, and do not have much cash to spend on this project. The idea was to design a SSTC (still not sure if I want to go for a DRSSTC or not) that your average hobbyist with little cash can build. I realize it may not be this simple, but that was the hope, anyway.

Okay, that makes sense. I am used to needing pull-up/pull-down resistors and did not realize they would not work in this case. The TC4420/9 do not have enable pins. Also, since one driver is inverting and one non-inverting, I thought they were always supposed to be opposite of each other, thus creating the +/- 5V oscillation on the primary of the GDT. So you're saying they should both be on or both be off when the interrupter is low? I guess I don't really see the logic in this.

Yes, that has been pointed out to me and quite honestly I'm not sure what I was thinking. I don't know why I used a grounded center tap, and I can see how it's horribly wrong =P

I have opted for the 1:1:1:1:1 transformer, as was suggested earlier. Unfortunately Proteus does not seem to have a model for this, so may have to start drawing it by hand and forgetting about the simulations. The first and third secondaries of the GDT will be in phase with the input, and the second and fourth secondaries will be out of phase. The first will be connected to the gate and source of the left high-side MOSFET, the second is connected to the right high-side MOSFET, the third will be connected to the right low-side MOSFET, and the fourth will be connected to the left low-side MOSFET. Does this sound right? I will be sketching it up eventually, and I will see about posting it again.

Okay, good. That's what I was planning on, so it's good to know I had *something* right (except for the turns ratio)!

Noted and added!

I originally had a 100nF capacitor connected to the CT output, I'm not sure what happened to it. I must have deleted it when I moved things around and forgot to put it back in. Would 100nF have been okay, or should it be closer to the 10nF you recommended? Someone also suggested I simply get rid of the zener and use a shottkey, or even simpler, two 4148s to clamp the output to the 5V rail. What are your thoughts on this?

Good point, and they have been noted.

Noted.

I had not thought of that until someone suggested it earlier. Now, correct me if I'm wrong, but a primary feedback signal is produced by putting a transformer in series with the primary, am I correct? And then I will need to rectify it and process it so that it passes a square wave back into the drivers?

Thanks again everyone for the great information. It certainly helps!

Cheers,

Matt

DerStrom8, Thu Jun 26 2014, 05:09PM

Excellent comments, Dr. Dark Current, thank you. This is why I came here--for replies like yours!

Dr. Dark Current wrote ...

I think the best way to get started is to build a proven design and then learn from it. I'd say this is the quickiest way to learn and then you'll be able to design a much better circuit.

I think the best way to get started is to build a proven design and then learn from it. I'd say this is the quickiest way to learn and then you'll be able to design a much better circuit.

The other issue I didn't mention was that I am limited for parts, and do not have much cash to spend on this project. The idea was to design a SSTC (still not sure if I want to go for a DRSSTC or not) that your average hobbyist with little cash can build. I realize it may not be this simple, but that was the hope, anyway.

Dr. Dark Current wrote ...

But anyway:

-Pulling the gate drivers' inputs low or high during OFF-time is wrong, you must make sure that both drivers outputs are LOW or both HIGH during the OFF-time. Use the ENABLE pins of G-drivers or NAND gates.

But anyway:

-Pulling the gate drivers' inputs low or high during OFF-time is wrong, you must make sure that both drivers outputs are LOW or both HIGH during the OFF-time. Use the ENABLE pins of G-drivers or NAND gates.

Okay, that makes sense. I am used to needing pull-up/pull-down resistors and did not realize they would not work in this case. The TC4420/9 do not have enable pins. Also, since one driver is inverting and one non-inverting, I thought they were always supposed to be opposite of each other, thus creating the +/- 5V oscillation on the primary of the GDT. So you're saying they should both be on or both be off when the interrupter is low? I guess I don't really see the logic in this.

Dr. Dark Current wrote ...

-The GDT connection is horribly wrong. Just look at any other SSTC design, they all use similar connection of GDT secondaries.

-The GDT connection is horribly wrong. Just look at any other SSTC design, they all use similar connection of GDT secondaries.

Yes, that has been pointed out to me and quite honestly I'm not sure what I was thinking. I don't know why I used a grounded center tap, and I can see how it's horribly wrong =P

I have opted for the 1:1:1:1:1 transformer, as was suggested earlier. Unfortunately Proteus does not seem to have a model for this, so may have to start drawing it by hand and forgetting about the simulations. The first and third secondaries of the GDT will be in phase with the input, and the second and fourth secondaries will be out of phase. The first will be connected to the gate and source of the left high-side MOSFET, the second is connected to the right high-side MOSFET, the third will be connected to the right low-side MOSFET, and the fourth will be connected to the left low-side MOSFET. Does this sound right? I will be sketching it up eventually, and I will see about posting it again.

Dr. Dark Current wrote ...

-The GDT should have a 1:1 turns ratio. Wind it by insulated wires twisted together (eg. wires from an UTP cable) to form a "stranded wire". This way you'll get the lowest leakage inductance.

-The GDT should have a 1:1 turns ratio. Wind it by insulated wires twisted together (eg. wires from an UTP cable) to form a "stranded wire". This way you'll get the lowest leakage inductance.

Okay, good. That's what I was planning on, so it's good to know I had *something* right (except for the turns ratio)!

Dr. Dark Current wrote ...

-Connect a 1-10uF ceramic/film cap in series with GDT primary to block DC voltage.

-Connect a 1-10uF ceramic/film cap in series with GDT primary to block DC voltage.

Noted and added!

Dr. Dark Current wrote ...

-Remove the resistor on CT output and replace it with a ~10nF capacitor to block DC voltage. The zener diode has a too high capacitance and it will increase your loop delay; use two 1N4148 diodes to clamp the CT output to the zener diode (to decrease capacitances).

-Remove the resistor on CT output and replace it with a ~10nF capacitor to block DC voltage. The zener diode has a too high capacitance and it will increase your loop delay; use two 1N4148 diodes to clamp the CT output to the zener diode (to decrease capacitances).

I originally had a 100nF capacitor connected to the CT output, I'm not sure what happened to it. I must have deleted it when I moved things around and forgot to put it back in. Would 100nF have been okay, or should it be closer to the 10nF you recommended? Someone also suggested I simply get rid of the zener and use a shottkey, or even simpler, two 4148s to clamp the output to the 5V rail. What are your thoughts on this?

Dr. Dark Current wrote ...

-Gate driver decoupling caps are not drawn but I suppose you'll use them.

-Gate driver decoupling caps are not drawn but I suppose you'll use them.

Good point, and they have been noted.

Dr. Dark Current wrote ...

-The bridge is missing its decoupling capacitor as well.

-The bridge is missing its decoupling capacitor as well.

Noted.

Dr. Dark Current wrote ...

-If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

-If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

I had not thought of that until someone suggested it earlier. Now, correct me if I'm wrong, but a primary feedback signal is produced by putting a transformer in series with the primary, am I correct? And then I will need to rectify it and process it so that it passes a square wave back into the drivers?

Thanks again everyone for the great information. It certainly helps!

Cheers,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 05:33PM

Also, you did want to power the gate drivers from 5 volts? NO, use 12 or 15 volts.

In this application, you can clamp the CT output to the 5V rail by two 1N4148 diodes. The current here is small. If the current would be larger, you would need to make sure the voltage of the 5V rail does not increase because of the additional rectified "supply current"; in this case it's best to clamp the input to the zener diode instead of the 5V supply.

Dr. Dark Current, Thu Jun 26 2014, 05:33PM

wrote ...

So you're saying they should both be on or both be off when the interrupter is low? I guess I don't really see the logic in this.

When the interrupter is disabled, there should be no voltage on the GDT primary. As you pointed out, the drivers by itself are always at opposite logic levels when the inputs are connected, so in this configuration they are unable to turn off the GDT.So you're saying they should both be on or both be off when the interrupter is low? I guess I don't really see the logic in this.

Also, you did want to power the gate drivers from 5 volts? NO, use 12 or 15 volts.

wrote ...

Would 100nF have been okay, or should it be closer to the 10nF you recommended? Someone also suggested I simply get rid of the zener and use a shottkey, or even simpler, two 4148s to clamp the output to the 5V rail. What are your thoughts on this?

I would use 10 nF but I guess it doesn't matter much. The 10 nF one will quicker block the DC voltage.Would 100nF have been okay, or should it be closer to the 10nF you recommended? Someone also suggested I simply get rid of the zener and use a shottkey, or even simpler, two 4148s to clamp the output to the 5V rail. What are your thoughts on this?

In this application, you can clamp the CT output to the 5V rail by two 1N4148 diodes. The current here is small. If the current would be larger, you would need to make sure the voltage of the 5V rail does not increase because of the additional rectified "supply current"; in this case it's best to clamp the input to the zener diode instead of the 5V supply.

wrote ...

Now, correct me if I'm wrong, but a primary feedback signal is produced by putting a transformer in series with the primary, am I correct? And then I will need to rectify it and process it so that it passes a square wave back into the drivers?

You use a CT in a similar configuration like your secondary base current sense, just pass the primary wire through it instead of the secondary ground. The current on the CT output will be increased of course, so the clamping circuit and nearby components would need to be modified. There are different ways of dealing with this.Now, correct me if I'm wrong, but a primary feedback signal is produced by putting a transformer in series with the primary, am I correct? And then I will need to rectify it and process it so that it passes a square wave back into the drivers?

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 05:37PM

I've been thinking guys, should I stick with the dual schmitt-trigger inverter to clean up the feedback, or should I opt for a zero-crossing detector instead? I'm just wondering if there's a way I can improve the signal conditioning section of the circuit.

DerStrom8, Thu Jun 26 2014, 05:37PM

I've been thinking guys, should I stick with the dual schmitt-trigger inverter to clean up the feedback, or should I opt for a zero-crossing detector instead? I'm just wondering if there's a way I can improve the signal conditioning section of the circuit.

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 06:03PM

The Schmitt trigger inverter is perfect for this job, I'm not aware of any better solution. And you can use only one inverter gate, two of them are not required.

Dr. Dark Current, Thu Jun 26 2014, 06:03PM

The Schmitt trigger inverter is perfect for this job, I'm not aware of any better solution. And you can use only one inverter gate, two of them are not required.

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 07:28PM

I see what you mean now. To this point I was using the interrupter to switch the phase, but I see now that that is not what I want to be doing. ONLY the feedback should be changing the phase, correct? That actually explains a lot of the confusion I was having. I was thinking of replacing the TC4420/9 with the UCC27425, which has an inverting and a non-inverting driver, but includes enable pins. I think that would be best in this case, as the interrupter would do its job correctly.

I'm sure I can get my hands on a 10nF capacitor, so I won't need to use a 100nF one.

Sounds good, I'll give that a try!

Would there be any benefit to using two? Obviously the signal wouldn't be inverted, but I don't know if that's really important. Of course, with two there will be more of a delay. I may just use one after all.

Thanks,

Matt

DerStrom8, Thu Jun 26 2014, 07:28PM

wrote ...

When the interrupter is disabled, there should be no voltage on the GDT primary. As you pointed out, the drivers by itself are always at opposite logic levels when the inputs are connected, so in this configuration they are unable to turn off the GDT.

Also, you did want to power the gate drivers from 5 volts? NO, use 12 or 15 volts.

When the interrupter is disabled, there should be no voltage on the GDT primary. As you pointed out, the drivers by itself are always at opposite logic levels when the inputs are connected, so in this configuration they are unable to turn off the GDT.

Also, you did want to power the gate drivers from 5 volts? NO, use 12 or 15 volts.

I see what you mean now. To this point I was using the interrupter to switch the phase, but I see now that that is not what I want to be doing. ONLY the feedback should be changing the phase, correct? That actually explains a lot of the confusion I was having. I was thinking of replacing the TC4420/9 with the UCC27425, which has an inverting and a non-inverting driver, but includes enable pins. I think that would be best in this case, as the interrupter would do its job correctly.

wrote ...

I would use 10 nF but I guess it doesn't matter much. The 10 nF one will quicker block the DC voltage.

In this application, you can clamp the CT output to the 5V rail by two 1N4148 diodes. The current here is small. If the current would be larger, you would need to make sure the voltage of the 5V rail does not increase because of the additional rectified "supply current"; in this case it's best to clamp the input to the zener diode instead of the 5V supply.

I would use 10 nF but I guess it doesn't matter much. The 10 nF one will quicker block the DC voltage.

In this application, you can clamp the CT output to the 5V rail by two 1N4148 diodes. The current here is small. If the current would be larger, you would need to make sure the voltage of the 5V rail does not increase because of the additional rectified "supply current"; in this case it's best to clamp the input to the zener diode instead of the 5V supply.

I'm sure I can get my hands on a 10nF capacitor, so I won't need to use a 100nF one.

wrote ...

You use a CT in a similar configuration like your secondary base current sense, just pass the primary wire through it instead of the secondary ground. The current on the CT output will be increased of course, so the clamping circuit and nearby components would need to be modified. There are different ways of dealing with this.

You use a CT in a similar configuration like your secondary base current sense, just pass the primary wire through it instead of the secondary ground. The current on the CT output will be increased of course, so the clamping circuit and nearby components would need to be modified. There are different ways of dealing with this.

Sounds good, I'll give that a try!

Dr. Dark Current wrote ...

The Schmitt trigger inverter is perfect for this job, I'm not aware of any better solution. And you can use only one inverter gate, two of them are not required.

The Schmitt trigger inverter is perfect for this job, I'm not aware of any better solution. And you can use only one inverter gate, two of them are not required.

Would there be any benefit to using two? Obviously the signal wouldn't be inverted, but I don't know if that's really important. Of course, with two there will be more of a delay. I may just use one after all.

Thanks,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 07:38PM

Yes two of them will just increase delay. You can change the phase by the CT connection. IIRC I've had some problems way back with 1 inverter gate producing false pulses, but that was probably just a bad layout. If your frequency is say below 300 kHz, you can use two gates, above that I would use one.

Dr. Dark Current, Thu Jun 26 2014, 07:38PM

Yes two of them will just increase delay. You can change the phase by the CT connection. IIRC I've had some problems way back with 1 inverter gate producing false pulses, but that was probably just a bad layout. If your frequency is say below 300 kHz, you can use two gates, above that I would use one.

Re: First SSTC design - Need some critique

DerStrom8, Thu Jun 26 2014, 11:29PM

Hi folks,

Just checking that I've done this right:

I will see about re-drawing my schematic so that it is more readable. I have been drawing it by hand, and I admit my handwriting is pretty awful!

So far, does everything sound correct? I believe I've followed your suggestions, but feel free to correct me if I misinterpreted them.

Cheers,

Matt

DerStrom8, Thu Jun 26 2014, 11:29PM

Hi folks,

Just checking that I've done this right:

- I am using a UCC27425 dual MOSFET driver, which contains one inverting and one non-inverting gate, as well as actual enable pins. I could probably still use the TC4420/9 with NAND gates, but I figure the smaller the better. This way I only need a single 8-pin DIP package.

- I have added a DC-blocking capacitor in series with the driver output to prevent it from shorting out the chip

- I am using a 1:1:1:1:1 GDT instead of a center-tapped one (which I realize was a terrible idea from the start)

- Two of the secondaries of the GDT are in-phase with the primary, and two are out of phase. Each secondary is connected (through a 10-ohm resistor to the gate of its corresponding FET (the in-phase windings are connected to the FETs diagonally opposite from each other in the H-bridge)

- I have added back-to-back 20V zener diodes between the gate and source of each FET to prevent voltage spikes from damaging them. I may opt for a TVS diode, but either should work ok

- I have added a decoupling capacitor between +50V and Ground in the H-bridge

- I added a 4.7uF film capacitor in series with the primary to also block DC

- Current transformer is simply a ferrite toroid transformer with ~50 windings for the feedback, and the primary coil wire is passed through the center

- One side of the CT output is grounded, the other is passed through a 10nF capacitor into a single Schmitt trigger inverter (7414)

- Between the capacitor and the schmitt trigger I have opted to use two Schottky diodes to clamp to the 5V rail, which is from a separate supply. It is well-regulated, so I would not worry too much about fluctuation, at least not to an extent that would cause problems

I will see about re-drawing my schematic so that it is more readable. I have been drawing it by hand, and I admit my handwriting is pretty awful!

So far, does everything sound correct? I believe I've followed your suggestions, but feel free to correct me if I misinterpreted them.

Cheers,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Thu Jun 26 2014, 11:47PM

Note: Schottky diodes have a relatively high capacitance. Using them to clamp the high current transformed from the primary winding is OK, but if you used them to clamp the CT sensing the secondary base current, you would again have problems with delays. In the second case, use 1N4148 signal diodes.

The other points seem correct.

Jan

Dr. Dark Current, Thu Jun 26 2014, 11:47PM

wrote ...

Current transformer is simply a ferrite toroid transformer with ~50 windings for the feedback, and the primary coil wire is passed through the center

One side of the CT output is grounded, the other is passed through a 10nF capacitor into a single Schmitt trigger inverter (7414)

The output current from the CT will be MUCH higher if you use primary feedback. Like 1 amp or more. Simply clamping to the 5V rail is not possible; the regulation of the supply plays no role here, what matters is that the supply cannot take reverse current. Wind more turns on the CT (like at least 100) and clamp the output using 1 amp Schottky diodes (1N5818) to a beefy ("5 watt") zener diode, which should have a voltage rating of about 4-4.7V. Connect a 100 ohm safety resistor in series with the Schmitt inverter's input. Because of the high current involved, increase the DC blocking capacitor size to 100nF (or rather 220nF).Current transformer is simply a ferrite toroid transformer with ~50 windings for the feedback, and the primary coil wire is passed through the center

One side of the CT output is grounded, the other is passed through a 10nF capacitor into a single Schmitt trigger inverter (7414)

Note: Schottky diodes have a relatively high capacitance. Using them to clamp the high current transformed from the primary winding is OK, but if you used them to clamp the CT sensing the secondary base current, you would again have problems with delays. In the second case, use 1N4148 signal diodes.

The other points seem correct.

Jan

Re: First SSTC design - Need some critique

DerStrom8, Fri Jun 27 2014, 12:53AM

I was wondering how the higher current on the feedback transformer would be handled. I see now what you meant regarding the 5v supply.

Now, when you suggest clamping the output to the zener using the schottkys, I guess I'm still a bit unclear as to how this would be connected...?

I'm not sure if I can get my hands on high-power zeners, but I will see what I can find.

In regards to the current transformer, someone recommended I use a 1:1000 transformer, which is created using two toroid cores, each wrapped with two (twisted) wires connected in such a way as to get 32 windings on each, and 1024 windings total (32*32). I'm wondering if I ought to go this route. What are your thoughts?

Thanks,

Matt

DerStrom8, Fri Jun 27 2014, 12:53AM

Dr. Dark Current wrote ...

The output current from the CT will be MUCH higher if you use primary feedback. Like 1 amp or more. Simply clamping to the 5V rail is not possible; the regulation of the supply plays no role here, what matters is that the supply cannot take reverse current. Wind more turns on the CT (like at least 100) and clamp the output using 1 amp Schottky diodes (1N5818) to a beefy ("5 watt") zener diode, which should have a voltage rating of about 4-4.7V. Connect a 100 ohm safety resistor in series with the Schmitt inverter's input. Because of the high current involved, increase the DC blocking capacitor size to 100nF (or rather 220nF).

Note: Schottky diodes have a relatively high capacitance. Using them to clamp the high current transformed from the primary winding is OK, but if you used them to clamp the CT sensing the secondary base current, you would again have problems with delays. In the second case, use 1N4148 signal diodes.

The other points seem correct.

Jan

The output current from the CT will be MUCH higher if you use primary feedback. Like 1 amp or more. Simply clamping to the 5V rail is not possible; the regulation of the supply plays no role here, what matters is that the supply cannot take reverse current. Wind more turns on the CT (like at least 100) and clamp the output using 1 amp Schottky diodes (1N5818) to a beefy ("5 watt") zener diode, which should have a voltage rating of about 4-4.7V. Connect a 100 ohm safety resistor in series with the Schmitt inverter's input. Because of the high current involved, increase the DC blocking capacitor size to 100nF (or rather 220nF).

Note: Schottky diodes have a relatively high capacitance. Using them to clamp the high current transformed from the primary winding is OK, but if you used them to clamp the CT sensing the secondary base current, you would again have problems with delays. In the second case, use 1N4148 signal diodes.

The other points seem correct.

Jan

I was wondering how the higher current on the feedback transformer would be handled. I see now what you meant regarding the 5v supply.

Now, when you suggest clamping the output to the zener using the schottkys, I guess I'm still a bit unclear as to how this would be connected...?

I'm not sure if I can get my hands on high-power zeners, but I will see what I can find.

In regards to the current transformer, someone recommended I use a 1:1000 transformer, which is created using two toroid cores, each wrapped with two (twisted) wires connected in such a way as to get 32 windings on each, and 1024 windings total (32*32). I'm wondering if I ought to go this route. What are your thoughts?

Thanks,

Matt

Re: First SSTC design - Need some critique

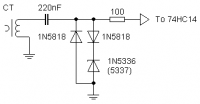

Dr. Dark Current, Fri Jun 27 2014, 08:03AM

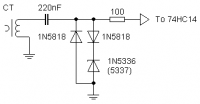

Like this

If you use a 1:1000 transformer, the current will be lower and you can then use a "standard 1.3-watt" Zener diode. It doesn't hurt to use your brain to solve such simple problems The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

Dr. Dark Current, Fri Jun 27 2014, 08:03AM

Like this

If you use a 1:1000 transformer, the current will be lower and you can then use a "standard 1.3-watt" Zener diode. It doesn't hurt to use your brain to solve such simple problems

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.Re: First SSTC design - Need some critique

Steve Conner, Fri Jun 27 2014, 09:18AM

Or how about the CT setup I use, a 1:33 (or 1:100 for larger coils) with two UF5408 type diodes for a burden. See top right of this schematic:

This gives about 2V p-p output at the usual primary current. I also use an ordinary burden resistor in series to drive a peak current meter, but this isn't necessary.

Steve Conner, Fri Jun 27 2014, 09:18AM

Or how about the CT setup I use, a 1:33 (or 1:100 for larger coils) with two UF5408 type diodes for a burden. See top right of this schematic:

This gives about 2V p-p output at the usual primary current. I also use an ordinary burden resistor in series to drive a peak current meter, but this isn't necessary.

Re: First SSTC design - Need some critique

DerStrom8, Fri Jun 27 2014, 11:24AM

Hmm, guess I was over-thinking the schematic

I knew a 1:1000 transformer would drop the current significantly more, my question was more about if there were any disadvantages compared to a 1:100 transformer.

@Steve Connor, your schematic actually popped up several times in my searches, and is one of the ones I've used for reference.

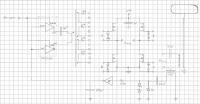

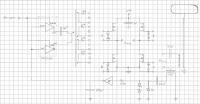

here is the updated schematic. Please excuse the crudity of this model. I didn't have time to build it to scale or paint it.

It reflects all of the changes you guys have suggested. Once again, feel free to let me know if I've missed something!

Thanks,

Matt

DerStrom8, Fri Jun 27 2014, 11:24AM

Dr. Dark Current wrote ...

Like this

If you use a 1:1000 transformer, the current will be lower and you can then use a "standard 1.3-watt" Zener diode. It doesn't hurt to use your brain to solve such simple problems The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

Like this

If you use a 1:1000 transformer, the current will be lower and you can then use a "standard 1.3-watt" Zener diode. It doesn't hurt to use your brain to solve such simple problems

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.

The current on the sec side is the current on the primary side divided by number of turns. The primary current is your design thing, then from this calculate the clamping circuit. Even with the 1:1000 CT I would still use a Zener diode and not clamp the output to the 5V supply.Hmm, guess I was over-thinking the schematic

I knew a 1:1000 transformer would drop the current significantly more, my question was more about if there were any disadvantages compared to a 1:100 transformer.

@Steve Connor, your schematic actually popped up several times in my searches, and is one of the ones I've used for reference.

here is the updated schematic. Please excuse the crudity of this model. I didn't have time to build it to scale or paint it.

It reflects all of the changes you guys have suggested. Once again, feel free to let me know if I've missed something!

Thanks,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Fri Jun 27 2014, 01:56PM

What does the cap on the output of the 74HC14 do? o_0

P.S. If you use the coil as an DRSSTC with no loop delay compensation (as your current circuit) I highly suggest you to use IGBTs with ultrafast antiparallel diodes rather than MOSFETs. This is because the switching transitions happen after current zero crossings, which forces recovery of the free-wheeling diodes. The body diodes of MOSFETs are relatively much too slow for this.

On the other hand, using it as a single-resonant SSTC, FETs are a better choice, because the magnetizing inductance of the primary moves the switching transitions before current zero crossings (usually).

Dr. Dark Current, Fri Jun 27 2014, 01:56PM

What does the cap on the output of the 74HC14 do? o_0

P.S. If you use the coil as an DRSSTC with no loop delay compensation (as your current circuit) I highly suggest you to use IGBTs with ultrafast antiparallel diodes rather than MOSFETs. This is because the switching transitions happen after current zero crossings, which forces recovery of the free-wheeling diodes. The body diodes of MOSFETs are relatively much too slow for this.

On the other hand, using it as a single-resonant SSTC, FETs are a better choice, because the magnetizing inductance of the primary moves the switching transitions before current zero crossings (usually).

Re: First SSTC design - Need some critique

DerStrom8, Fri Jun 27 2014, 02:49PM

The 100pF cap filters out the extremely high frequencies that I don't really want going into the 27425. It's not critical, but one of those "nice to have" things.

You actually bring up a point that I have been considering. To this point I have been designing this coil around MOSFETs because it's what I have in my parts bin. I realize they are slower and probably not the best for high-frequency circuits, so if I do turn this into a DRSSTC I will swap them out with IGBTs. For the time being, though, I think I'll just stick with the MOSFETs and get a working TC. I can then make modifications from there.

Oh, and they are not shown in the schematic, but yes--each of the chips (the UCC27425 and the 7414) have decoupling caps. I simply opted not to show the power pins on the schematic, so I did not show the caps.

Thanks,

Matt

DerStrom8, Fri Jun 27 2014, 02:49PM

Dr. Dark Current wrote ...

What does the cap on the output of the 74HC14 do? o_0

P.S. If you use the coil as an DRSSTC with no loop delay compensation (as your current circuit) I highly suggest you to use IGBTs with ultrafast antiparallel diodes rather than MOSFETs. This is because the switching transitions happen after current zero crossings, which forces recovery of the free-wheeling diodes. The body diodes of MOSFETs are relatively much too slow for this.

On the other hand, using it as a single-resonant SSTC, FETs are a better choice, because the magnetizing inductance of the primary moves the switching transitions before current zero crossings (usually).

What does the cap on the output of the 74HC14 do? o_0

P.S. If you use the coil as an DRSSTC with no loop delay compensation (as your current circuit) I highly suggest you to use IGBTs with ultrafast antiparallel diodes rather than MOSFETs. This is because the switching transitions happen after current zero crossings, which forces recovery of the free-wheeling diodes. The body diodes of MOSFETs are relatively much too slow for this.

On the other hand, using it as a single-resonant SSTC, FETs are a better choice, because the magnetizing inductance of the primary moves the switching transitions before current zero crossings (usually).

The 100pF cap filters out the extremely high frequencies that I don't really want going into the 27425. It's not critical, but one of those "nice to have" things.

You actually bring up a point that I have been considering. To this point I have been designing this coil around MOSFETs because it's what I have in my parts bin. I realize they are slower and probably not the best for high-frequency circuits, so if I do turn this into a DRSSTC I will swap them out with IGBTs. For the time being, though, I think I'll just stick with the MOSFETs and get a working TC. I can then make modifications from there.

Oh, and they are not shown in the schematic, but yes--each of the chips (the UCC27425 and the 7414) have decoupling caps. I simply opted not to show the power pins on the schematic, so I did not show the caps.

Thanks,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Fri Jun 27 2014, 05:18PM

MOSFETs are faster devices than IGBTs. It's just their body diode which is slow. However the FETs can not take such high pulsed currents, so they are better for coils with lower peak powers and higher duty cycles.

I don't see why you do want to slow down the transitions into the gate drivers. Having them as fast as possible is not a bad thing, often it is required. The cap will just increase your loop delay and present unnecessary load onto the inverter gate's output.

Dr. Dark Current, Fri Jun 27 2014, 05:18PM

MOSFETs are faster devices than IGBTs. It's just their body diode which is slow. However the FETs can not take such high pulsed currents, so they are better for coils with lower peak powers and higher duty cycles.

I don't see why you do want to slow down the transitions into the gate drivers. Having them as fast as possible is not a bad thing, often it is required. The cap will just increase your loop delay and present unnecessary load onto the inverter gate's output.

Re: First SSTC design - Need some critique

DerStrom8, Fri Jun 27 2014, 08:26PM

The 100pF cap is supposed to filter out the MHz harmonics, but can be omitted if necessary. I actually borrowed it from loneocean's SSTC2 design.

I have always found IGBTs to be more expensive than MOSFETs, but I came across something once that said it was the other way around? The MOSFETs I have now are junk-bin ones and are really only going to be used for testing. They're IRF350s in TO-3 packages. The datasheets say they are rated for 400V @14A, though the on resistance is quite high--0.3 ohms--and I'm not certain about the switching frequency. The datasheet says it has a 35nS turn-on time and a 150nS turn-off time, so if I did my math right it should be able to switch fast enough, though I'm not 100% sure on this. Eventually I do hope to swap all of them out with proper IGBTs.

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

DerStrom8, Fri Jun 27 2014, 08:26PM

Dr. Dark Current wrote ...

MOSFETs are faster devices than IGBTs. It's just their body diode which is slow. However the FETs can not take such high pulsed currents, so they are better for coils with lower peak powers and higher duty cycles.

I don't see why you do want to slow down the transitions into the gate drivers. Having them as fast as possible is not a bad thing, often it is required. The cap will just increase your loop delay and present unnecessary load onto the inverter gate's output.

MOSFETs are faster devices than IGBTs. It's just their body diode which is slow. However the FETs can not take such high pulsed currents, so they are better for coils with lower peak powers and higher duty cycles.

I don't see why you do want to slow down the transitions into the gate drivers. Having them as fast as possible is not a bad thing, often it is required. The cap will just increase your loop delay and present unnecessary load onto the inverter gate's output.

The 100pF cap is supposed to filter out the MHz harmonics, but can be omitted if necessary. I actually borrowed it from loneocean's SSTC2 design.

I have always found IGBTs to be more expensive than MOSFETs, but I came across something once that said it was the other way around? The MOSFETs I have now are junk-bin ones and are really only going to be used for testing. They're IRF350s in TO-3 packages. The datasheets say they are rated for 400V @14A, though the on resistance is quite high--0.3 ohms--and I'm not certain about the switching frequency. The datasheet says it has a 35nS turn-on time and a 150nS turn-off time, so if I did my math right it should be able to switch fast enough, though I'm not 100% sure on this. Eventually I do hope to swap all of them out with proper IGBTs.

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

Re: First SSTC design - Need some critique

Dr. Dark Current, Fri Jun 27 2014, 10:52PM

Primary feedback will not work in an SSTC, I thought this has been already said a bit.

-> If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

Dr. Dark Current, Fri Jun 27 2014, 10:52PM

Primary feedback will not work in an SSTC, I thought this has been already said a bit.

-> If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

Re: First SSTC design - Need some critique

loneoceans, Fri Jun 27 2014, 10:57PM

I think there a little bit of confusion in the thread since you mentioned you wanted to build a DRSSTC at the beginning. I'd recommend going with an SSTC first since it's just easier to get running. For DRSSTCs, primary feedback is usually used, and secondary for normal SSTCs (as you mentioned, no resonance going on in the primary for a normal SSTC, so you cannot use pri feedback). In fact, antenna works pretty well too in my experience. I never encountered any problems with or without the 100pF cap so no need to put it in. You don't need a bit GDT for your full bridge (and they're not expensive either) - just a few dollars online for a 1" core which will be enough for you if you use thinner wire.

If I had a small core, I'd wind it with 6 thin wires twisted together. 4 of them go to the transistors, and two of them will be in parallel and wired to the driver. Just make sure your phasing it correct! For sure you could wind two cores - it'll be exactly as described on my page, with the primaries in parallel. Or you could just go for a half bridge first which will save you half of the parts! Again most of the components are really not expensive - suitable IGBTs or MOSFETs all run for around $3 or less on digikey which would work great!

There are several reasons why people like IGBTs for DRSSTC use because of the lower losses (proportional to I in IGBTs but squared for mosfets), higher current handling capability and usually nice fast integrated body diodes. As Dr. Spark said, they're also usually slower, but some of the nice new ones on the market today are approaching the speeds of older Mosfets! I've pushed TO220 igbts to 800kHz in DRSSTC operation and they seem to be fine. :o

loneoceans, Fri Jun 27 2014, 10:57PM

DerStrom8 wrote ...

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

I think there a little bit of confusion in the thread since you mentioned you wanted to build a DRSSTC at the beginning. I'd recommend going with an SSTC first since it's just easier to get running. For DRSSTCs, primary feedback is usually used, and secondary for normal SSTCs (as you mentioned, no resonance going on in the primary for a normal SSTC, so you cannot use pri feedback). In fact, antenna works pretty well too in my experience. I never encountered any problems with or without the 100pF cap so no need to put it in. You don't need a bit GDT for your full bridge (and they're not expensive either) - just a few dollars online for a 1" core which will be enough for you if you use thinner wire.

If I had a small core, I'd wind it with 6 thin wires twisted together. 4 of them go to the transistors, and two of them will be in parallel and wired to the driver. Just make sure your phasing it correct! For sure you could wind two cores - it'll be exactly as described on my page, with the primaries in parallel. Or you could just go for a half bridge first which will save you half of the parts! Again most of the components are really not expensive - suitable IGBTs or MOSFETs all run for around $3 or less on digikey which would work great!

There are several reasons why people like IGBTs for DRSSTC use because of the lower losses (proportional to I in IGBTs but squared for mosfets), higher current handling capability and usually nice fast integrated body diodes. As Dr. Spark said, they're also usually slower, but some of the nice new ones on the market today are approaching the speeds of older Mosfets! I've pushed TO220 igbts to 800kHz in DRSSTC operation and they seem to be fine. :o

Re: First SSTC design - Need some critique

DerStrom8, Fri Jun 27 2014, 11:16PM

I had a feeling that was the cause of the confusion. I should have specified that I am starting with an ordinary SSTC and eventually will probably modify it later on to be a DRSSTC. I apologize for misleading you. Since this is the case, I will be using the secondary feedback (which makes much more sense to me! ) that I originally planned on. I will probably change it when I convert it into a DRSSTC.

) that I originally planned on. I will probably change it when I convert it into a DRSSTC.

I found examples of people using Ethernet wires for the GDT, which I think I may do--they are cheap and easy to source, and there are 8 wires in each cable already. I will probably do the same for the secondary feedback winding.

Again, this is all great info, so thanks very much!

Cheers,

Matt

I understand how the losses tend to be more significant in MOSFETs. Some day (hopefully soon) I will look into getting some IGBTs, but again, I already have some FETs that will probably work, so I may as well just start with them

DerStrom8, Fri Jun 27 2014, 11:16PM

Dr. Dark Current wrote ...

Primary feedback will not work in an SSTC, I thought this has been already said a bit.

-> If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

Primary feedback will not work in an SSTC, I thought this has been already said a bit.

-> If the circuit is to be used as an DRSSTC, a primary current feedback is a much better option than secondary base current feedback.

loneoceans wrote ...

I think there a little bit of confusion in the thread since you mentioned you wanted to build a DRSSTC at the beginning. I'd recommend going with an SSTC first since it's just easier to get running. For DRSSTCs, primary feedback is usually used, and secondary for normal SSTCs (as you mentioned, no resonance going on in the primary for a normal SSTC, so you cannot use pri feedback). In fact, antenna works pretty well too in my experience. I never encountered any problems with or without the 100pF cap so no need to put it in. You don't need a bit GDT for your full bridge (and they're not expensive either) - just a few dollars online for a 1" core which will be enough for you if you use thinner wire.

If I had a small core, I'd wind it with 6 thin wires twisted together. 4 of them go to the transistors, and two of them will be in parallel and wired to the driver. Just make sure your phasing it correct! For sure you could wind two cores - it'll be exactly as described on my page, with the primaries in parallel. Or you could just go for a half bridge first which will save you half of the parts! Again most of the components are really not expensive - suitable IGBTs or MOSFETs all run for around $3 or less on digikey which would work great!

There are several reasons why people like IGBTs for DRSSTC use because of the lower losses (proportional to I in IGBTs but squared for mosfets), higher current handling capability and usually nice fast integrated body diodes. As Dr. Spark said, they're also usually slower, but some of the nice new ones on the market today are approaching the speeds of older Mosfets! I've pushed TO220 igbts to 800kHz in DRSSTC operation and they seem to be fine. :o

I think there a little bit of confusion in the thread since you mentioned you wanted to build a DRSSTC at the beginning. I'd recommend going with an SSTC first since it's just easier to get running. For DRSSTCs, primary feedback is usually used, and secondary for normal SSTCs (as you mentioned, no resonance going on in the primary for a normal SSTC, so you cannot use pri feedback). In fact, antenna works pretty well too in my experience. I never encountered any problems with or without the 100pF cap so no need to put it in. You don't need a bit GDT for your full bridge (and they're not expensive either) - just a few dollars online for a 1" core which will be enough for you if you use thinner wire.

If I had a small core, I'd wind it with 6 thin wires twisted together. 4 of them go to the transistors, and two of them will be in parallel and wired to the driver. Just make sure your phasing it correct! For sure you could wind two cores - it'll be exactly as described on my page, with the primaries in parallel. Or you could just go for a half bridge first which will save you half of the parts! Again most of the components are really not expensive - suitable IGBTs or MOSFETs all run for around $3 or less on digikey which would work great!

There are several reasons why people like IGBTs for DRSSTC use because of the lower losses (proportional to I in IGBTs but squared for mosfets), higher current handling capability and usually nice fast integrated body diodes. As Dr. Spark said, they're also usually slower, but some of the nice new ones on the market today are approaching the speeds of older Mosfets! I've pushed TO220 igbts to 800kHz in DRSSTC operation and they seem to be fine. :o

I had a feeling that was the cause of the confusion. I should have specified that I am starting with an ordinary SSTC and eventually will probably modify it later on to be a DRSSTC. I apologize for misleading you. Since this is the case, I will be using the secondary feedback (which makes much more sense to me!

) that I originally planned on. I will probably change it when I convert it into a DRSSTC.

) that I originally planned on. I will probably change it when I convert it into a DRSSTC. I found examples of people using Ethernet wires for the GDT, which I think I may do--they are cheap and easy to source, and there are 8 wires in each cable already. I will probably do the same for the secondary feedback winding.

Again, this is all great info, so thanks very much!

Cheers,

Matt

I understand how the losses tend to be more significant in MOSFETs. Some day (hopefully soon) I will look into getting some IGBTs, but again, I already have some FETs that will probably work, so I may as well just start with them

Re: First SSTC design - Need some critique

GrantX, Sat Jun 28 2014, 06:16AM

http://thedatastream.4hv.org/gdt_index.htm This site has been invaluable in helping me understand proper GDT design. It covers the important theory elements, as well as core selection and winding techniques. Very nice to keep in your bookmarks.

EDIT: Sorry, I didn't see that your questions regarding feedback had already been answered.

You're definitely getting there.

Primary feedback: DRSSTC - both the primary and secondary are resonant tank circuits, ideally both tuned to almost the same frequency. In a DRSSTC you need to see how far the primary current is ringing up; since the inverter is switching at the primary circuit's resonant frequency the current gets bigger each half cycle (the simplified version as I currently understand it, I'm still learning as well).

Secondary base feedback: standard SSTC - only the secondary is being driven at it's resonant frequency, thus the primary current stays pretty much steady. Less turns on the primary means less impedance and thus more input current. Again, simplified version.

Designing a single-resonant SSTC seems very similar to other "normal" switch mode power supplies.

GrantX, Sat Jun 28 2014, 06:16AM

DerStrom8 wrote ...

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

Hi again, I've been thinking--

Shouldn't the feedback match the frequency of the secondary? If so, how would primary feedback work in a regular SSTC if it is not actually in tune with the secondary? I guess this is a little confusing to me.

On another note, do you have recommendations for winding the GDT? I'm thinking of making two transformers with paralleled primaries, and two secondaries on each core. The other option would be to wind all of the coils on one core, but I think that would require a larger toroid, which would be more expensive. I'm just wondering how other people have wound their GDTs.

Thanks for all the help guys, things are really coming together now.

Regards,

Matt

http://thedatastream.4hv.org/gdt_index.htm This site has been invaluable in helping me understand proper GDT design. It covers the important theory elements, as well as core selection and winding techniques. Very nice to keep in your bookmarks.

EDIT: Sorry, I didn't see that your questions regarding feedback had already been answered.

You're definitely getting there.

Primary feedback: DRSSTC - both the primary and secondary are resonant tank circuits, ideally both tuned to almost the same frequency. In a DRSSTC you need to see how far the primary current is ringing up; since the inverter is switching at the primary circuit's resonant frequency the current gets bigger each half cycle (the simplified version as I currently understand it, I'm still learning as well).

Secondary base feedback: standard SSTC - only the secondary is being driven at it's resonant frequency, thus the primary current stays pretty much steady. Less turns on the primary means less impedance and thus more input current. Again, simplified version.

Designing a single-resonant SSTC seems very similar to other "normal" switch mode power supplies.

Re: First SSTC design - Need some critique

Steve Conner, Sat Jun 28 2014, 12:25PM

If you want to use that 100pF capacitor to filter out high frequencies, it should probably be on the input of the logic gate, not the output.

Steve Conner, Sat Jun 28 2014, 12:25PM

If you want to use that 100pF capacitor to filter out high frequencies, it should probably be on the input of the logic gate, not the output.

Re: First SSTC design - Need some critique

DerStrom8, Sat Jun 28 2014, 12:49PM

I'll definitely take a look at the link, thank you very much!

Yes, I understand why you'd want to use a feedback transformer on the primary in a DRSSTC and why you can't on a regular SSTC. For a little while I was thinking I had mentioned that I wanted to start with a regular SSTC (which apparently I hadn't yet) and someone recommended a primary feedback transformer, and I couldn't understand how that would work. I see that it was a lack of communication on my part though, so things seem to fit my understanding and assumptions better now.

It's funny you should mention SMPSs--Every time I look at a SSTC schematic I think of a SMPS, and vice versa. They are very similar in a lot of ways. Just another idea of Tesla's that's leaked into modern technology! He really was the inventor of modern electronics

This has been noted, thank you!

I just need to get a few more parts and I should be able to start prototyping and testing before doing the full build.

Hi all, just thought I'd post some of my calculations here to make sure I'm doing things right.

Years ago I built a spark gap Tesla coil and I hope to re-use the secondary from it. The coil is about 19 inches tall wound around 4" ID PVC, giving the coil a diameter of about 4.5". Calculating the inductance using the formula,

L = (r^2 * t^2)/(9*r+10*l)

where L is the inductance, r is the radius, t is the # of turns, and l is the length, I get an inductance of 34.54mH.

For the topload I plan on starting with some aluminum dryer duct (also the same topload I used on my SGTC) with has a large diameter of 12.5" and a small diameter/height of 4 inches. This gives me a calculated capacitance of around 13.9pF.

Then, using the formula

f = 1/(2*pi*(L*C)^(1/2))

where f is the frequency, L is the inductance, and C is the capacitance, I get a resonant frequency of around 230KHz. I think this will probably be reasonable. How do you guys feel about these figures?

Cheers,

Matt

DerStrom8, Sat Jun 28 2014, 12:49PM

GrantX wrote ...